-

-

学生向け無料ソフトウェアにアクセス

Ansysは次世代の技術者を支援します

学生は、世界クラスのシミュレーションソフトウェアに無料でアクセスできます。

-

今すぐAnsysに接続!

未来をデザインする

Ansysに接続して、シミュレーションが次のブレークスルーにどのように貢献できるかを確認してください。

国および地域

無料トライアル

製品およびサービス

リソースとトレーニング

当社について

Back

製品およびサービス

Ansysブログ

October 10, 2019

クロストークとは電磁界の課題とトレンド

クロストークとは

クロストークとは、ある回路または伝送線からの信号が、隣接する回路または伝送線に干渉する現象です。それぞれの信号によって異なる電磁界が発生します。これらの信号や回路が互いの近くに配置されている場合、それらの電磁界が重なり合います。この干渉により、不要な信号結合が発生し、クロストークが生じます。クロストークは、プリント回路基板(PCB)、集積回路(IC)、通信ケーブルなどの電子システムで発生します。

エンジニアは、もはや電磁クロストークを無視できません。クロストークとは何かを理解し、特定して修正する方法を理解しなければなりません。

干渉を引き起こす電磁信号はアグレッサーと呼ばれ、クロストークの影響を受ける電磁信号はヴィクティムと呼ばれます。クロストークは次の2つのメカニズムによって発生します。

- 電界による容量性クロストーク

- 磁界による誘導性クロストーク

クロストークの例

プリント回路基板(PCB): PCBは、複数のトレースが互いに近接して配置される複雑な回路設計を伴います。高周波信号がトレースを通過する際、容量結合または誘導結合によって隣接するトレースに電圧が誘導され、クロストークが発生します。

集積回路(IC): さまざまなコンポーネントやインターコネクトが集積回路に密に実装されています。ICの一部で(トランジスタスイッチングにより)発生した電磁ノイズが、隣接するコンポーネントと結合したときにクロストークが生じ、性能を低下させます。

通信ケーブル: イーサネットケーブルなどの通信ケーブルでは、複数のツイストペアによってデータが伝送されます。撚りが不十分な場合、あるいはケーブルのシールドが不十分な場合、1つのツイストペアからの信号が隣接するペアでクロストークを引き起こし、データの破損や信号品質の低下につながります。

高速データ伝送: HDMIケーブルやUSBケーブルなどを使用した高速データ伝送では、信号が高周波で互いに干渉することがあります。この干渉によりクロストークが発生し、信号品質が低下します。

RFシステム: 高周波(RF)システムでは、隣接するアンテナまたはRF伝送線間でクロストークが発生することがあります。その結果、信号の干渉が生じ、システムの有効性が低下します。

SoCにおけるクロストーク

システムオンチップ(SoC)アーキテクチャを開発するエンジニアがクロストークを無視すれば、大きなリスクとなります。クロストークは電子設計エラーにつながり、最終的には市場投入の遅れやコストの超過につながります。

電磁クロストークを特定するための課題

電磁クロストーク解析の複雑さを理解するために、この問題を容量結合と対比させることができます。

容量結合は、近接する信号線間では強く、離れた信号線間では弱くなります。そのため、遠く離れた信号線間の容量結合を無視しても問題ありません。対照的に、誘導電磁結合は、比較的離れた信号間では無視できません。

電磁クロストークが問題の原因であるかどうかを判断するのは難しいことです。

電磁クロストークはより困難な問題です。まず、問題の症状が1つの指標(タイミング故障など)に現れないことです。多くの状況で、クロストークは、設計ごとに異なるいくつかの主要性能基準の低下として現れます。したがって、問題の原因をクロストークとして特定することが最初の課題となります。

さらに複雑にするのは、クロストークには通常、デジタル、アナログ、および高周波(RF)ブロック間の不要な結合が伴う点です。どちらがアグレッサーであり、ヴィクティムであるかを特定しなければなりません。

電磁クロストークは、設計ごとに異なる方法で特定、デバッグ、解決する必要があります。従来のソリューションでは、問題を引き起こす動作モードを防ぐアーキテクチャまたはソフトウェアのトリックを用いて解決していました。しかし、設計が複雑かつ高速になったため、その方法ではコスト的にも技術的にも不可能になりつつあります。

電磁クロストークをモデル化するための課題

電磁クロストークを正確にモデル化するためには、エンジニアは次のような非常に複雑な物理構造を解析し、モデル化する必要があります。

- 対象となるネット

- クロストークに寄与する周辺構造

- 電源およびグランド配線層

- バルクシリコン基板

- パッケージ層

- ボンド/バンプパッド

- 配線層

- シールリング

- メタルフィル

- デカップリングキャパシタ

電磁クロストークのモデル化では、すべてのコンポーネントを含める必要があるため、複雑になります。

これらの構造の多くは、物理的に複雑なレイアウトをしており、抵抗、静電容量、インダクタンス、結合容量、相互インダクタンスをシミュレーションするためには、大きなメッシュが必要です。

クロストークモデルのサイズを増大させる2つ目のモデリング要因は、エンジニアが設計内の小さな境界ボックスだけに着目して電磁クロストークを解析できないことです。電気容量結合の評価には、近隣のヴィクティム信号の解析は有効です。しかし、磁界が大きなループに沿って移動する、ヴィクティム信号のすぐ近くで形成される、あるいはチップのレイアウト全体を完全に囲むことがあります。

さらに、電磁クロストークツールで生成されるモデルのサイズを制限することは困難です。なぜなら、クロストーク問題の原因となるすべてのネットと、回路の性能を低下させる可能性のあるすべてのネットおよび構造を含める必要があるからです。

開発の下流で役に立つためには、次のようなクロストークモデルが必要です。

- Simulation Program with Integrated Circuit Emphasis(SPICE)で素早く計算できる

- SPICE環境で、さまざまな非線形およびノイズシミュレーションを実行できる

- ブロックやシリコンダイの境界を越えるデータベースに存在する

この3つの要件は、クロストークモデルの典型的なサイズと複雑さを考えると、満たすのは難しいと言えます。

SoCにおける電磁クロストーク解析の必要性の高まり

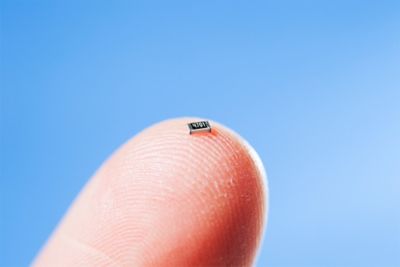

電子システムの帯域幅の拡大とサイズの縮小への要求が高まる中、エンジニアにとって電磁クロストークは大きな懸念事項です。こうした要求により、高速回路と広帯域チャネルが近くに配置されることが多くなります。

エレクトロニクスが小型になるにつれて、クロストークが大きな問題となります。

さらに、内部クロック周波数の継続的な上昇(5~10GHz)とデータ転送速度の上昇(10Gbps以上)もクロストークの問題を増幅させています。

つまり、高速で小型なエレクトロニクスではクロストークが生じやすくなりますが、寄生インダクタンスや誘導結合を無視できないようなSoCに対する需要が高まっています。

クロストークが発生しやすいSoCアーキテクチャ

クロストークの原因となるアーキテクチャやアプリケーションの設計トレンドは数多くあります。

たとえば、電磁クロストークは周波数に依存します。しかし、エンジニアは対象となる周波数のみに対して電磁クロストークを解析できません。

たとえば、立ち上がり時間と立ち下がり時間が速いクロック信号には、顕著な高調波周波数成分が含まれています。つまり、10GHzで動作するクロックには、50GHzで動作する第5高調波周波数成分があります。

同一システムで複数のイーサネットレーンを使用すると、クロストークの問題が複雑化します。

しかし、オンチップのクロック周波数を25GHzにしようとすると、マイクロ波周波数に相当する第3高調波をいかに安全にモデル化するかが課題となります。

電磁クロストークは、信号の大きさやノイズレベルに影響します。したがって、クロストークの影響は、SoCアプリケーションの低消費電力化に伴う信号電圧レベルの低下とノイズに対する感度の増大によって、さらに悪化します。

イーサネット、ファイバーチャネル、およびPeripheral Component Interconnect(PCI)もクロストークの原因となる可能性があります。高いデータ転送速度を実現するために、これらのバスでは並列に動作する複数のシリアルレーンを採用しています。たとえば、100Gbpsイーサネットでは、それぞれが10Gbpsで動作する10のチャネルを実装しています。単一システムに多数の高速シリアルレーンが実装されている場合、どのレーンもアグレッサーまたはヴィクティムにも成り得るため、クロストークの問題は複雑になります。

電磁クロストークが発生する可能性を高めるアーキテクチャの他のトレンドとして、以下のものがあります。

- 単一のSoC上の高速アナログブロック

- 位相同期回路(PLL: Phase Locked Loop)や電圧制御発振器(VCO: Voltage Controlled Oscillator)など

- 同一チップに実装された複数の高速クロックネットワーク

- クロックは必ずしも高い周波数で動作する必要はなく、10GHzで動作するヴィクティムクロックが2GHzで動作するアグレッサークロックの影響を受けることもあります。

- 高速デジタルブロックに隣接するRFまたは高速アナログブロック

- 共用のグランドネットやシリコン基板をグランドとしてタップすることはできません。

- これまでと同様、シリコン基板がブロック間の主要なノイズ伝播チャネルです。

- ファウンドリで挿入されるシールリングとスクライブライン

- S/Nマージンが小さい低電力設計

- クロストークのグリッチによって設定される高感度なコントロール/リセット信号

- ファンアウト方式のウエハレベルパッケージング集積技術

- 複数のダイが近接していると、電磁クロストークが発生する可能性が高くなります。

- 複数のダイが近接していると、電磁クロストークが発生する可能性が高くなります。

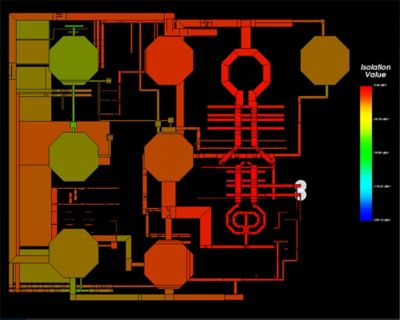

クロストークソリューション

SoCの集積では、高速デジタル回路、アナログブロック、RFブロックが近くに配置されます。そのため、これらのコンポーネントの内部やブロック間でクロストークが発生する可能性があります。

ほとんどの電子設計自動化(EDA)ツールは、デジタル、アナログ、またはRFコンポーネントの設計など、特定の設計タイプに合わせて調整されています。しかし、クロストークは特定のコンポーネント内だけで発生するわけではありません。

Ansys Pharosは、エンジニアがクロストークを特定するのに役立ちます。

IC設計エンジニアは、サインオフ段階で結合効果を予測する必要があります。IC設計者は、Ansys RaptorHを使用することで、設計階層内のさまざまなブロック間での電磁結合効果を正確に予測して、未知のクロストークを簡単に捉えることができます。

クロストークの詳細については、次の記事をご覧ください。高速シリアルリンクのクロストーク対策