クイックスペック

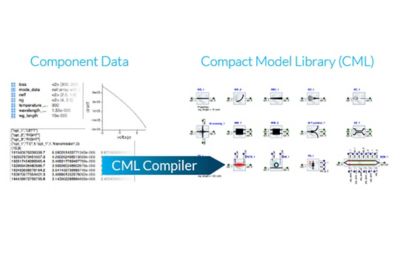

Lumerical CML Compilerは、測定やシミュレーションデータが集約された単一ソースから高品質のINTERCONNECTおよびVerilog-Aフォトニックコンパクトモデルを効率的に作成する方法を提供します。

Ansysは次世代の技術者を支援します

学生は、世界クラスのシミュレーションソフトウェアに無料でアクセスできます。

未来をデザインする

Ansysに接続して、シミュレーションが次のブレークスルーにどのように貢献できるかを確認してください。

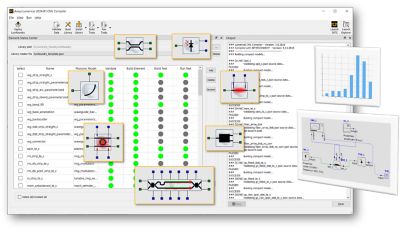

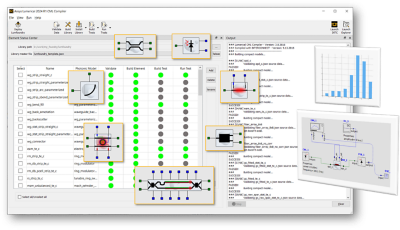

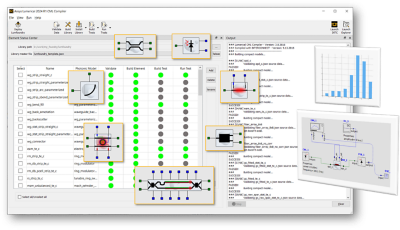

Ansys Lumerical CML Compilerでは、実証された自動クロスプラットフォームモデルジェネレータにより、コンパクトモデルライブラリ(CML: Compact Model Library)を自動的に作成できます。

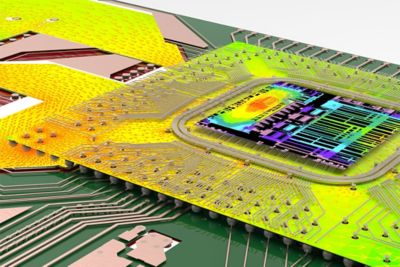

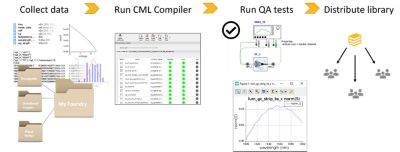

CMLを確実に構築、維持

実績と信頼性を備えたLumerical CML Compilerを使用して、コンパクトモデルライブラリ(CML)を効率的に作成できます。Lumerical CML Compilerは、単一データソースからのINTERCONNECTおよびVerilog-Aコンパクトモデルライブラリの作成、校正、メンテナンス、QAテストを自動化します。光源データは、実験での測定、2D/3D物理シミュレーション、またはそれらの組み合わせから取得できます。

Lumerical CML Compilerは、測定やシミュレーションデータが集約された単一ソースから高品質のINTERCONNECTおよびVerilog-Aフォトニックコンパクトモデルを効率的に作成する方法を提供します。

2026年3月

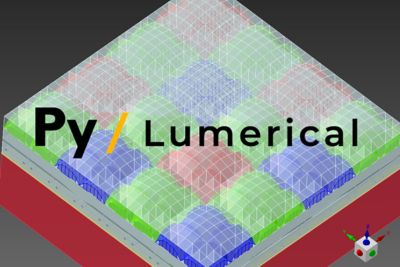

2026 R1リリースのAnsys Lumerical CML Compilerでは、IBIS-AMI次数低減モデル、操作性に優れた組込みモデルデータエディタ、PyLumericalを使用したツールの自動化といった機能が追加されています。

機械学習を使用してIBIS-AMIモデルを作成するための革新的なソリューションです。フォトニクスエンジニアはLumerical INTERCONNECTを使用して次数低減モデルを作成できるようになり、システム設計者は正確なシグナルインテグリティ解析と高速インターフェースシミュレーションを自信を持って実行できるようになります。

PythonベースのソリューションであるPyLumericalを使用して、Lumericalツールをシームレスに自動化できます。PyAnsysエコシステムと完全に互換性があり、FDTD、MODE、マルチフィジックス、INTERCONNECT、さらにはoptiSLangやSpeosなど、AnsysのツールやオープンソースのPythonライブラリと統合できます。この最新の効率的なアプローチにより、ワークフローを簡素化して、マルチフィジックスシミュレーションを強化できます。

Ansys Lumerical CML Compilerに組み込まれているモデルデータエディタは、GUIでデータを直接表示および編集するためのインタラクティブで操作性に優れたインターフェースです。マトリクスエディタとベクトルエディタが統合されたマルチタブ編集機能を備えており、多様なフォトニクスモデルを扱うための理想的なツールとして、CML Compilerを使い始めるユーザーに最適です。

機能

CML Compilerは、測定結果と3Dシミュレーション結果が集約された単一データソースからのINTERCONNECTおよびVerilog-Aフォトニックコンパクトモデルライブラリ(CML)の作成、メンテナンス、QAテストを自動化します。

CML Compilerでは、フォトニックPDKのための正確なフォトニックコンパクトモデルの作成が簡素化され、光集積回路を設計できるようになります。

Lumericalの最高技術責任者であるJames Pond博士が、CML Compilerのルーツおよび開発から、OFC 2020でデモが予定されている新しい統計解析およびシミュレーション機能まで紹介します。

Ansysは、障がいを持つユーザーを含め、あらゆるユーザーが当社製品にアクセスできることがきわめて重要であると考えています。この信念のもと、US Access Board(第508条)、Web Content Accessibility Guidelines(WCAG)、およびVoluntary Product Accessibility Template(VPAT)の最新フォーマットに基づくアクセシビリティ要件に準拠するよう努めています。

エンジニアリング課題に直面している場合は、当社のチームが支援します。豊富な経験と革新へのコミットメントを持つ当社に、ぜひご連絡ください。協力して、エンジニアリングの障害を成長と成功の機会に変えましょう。ぜひ今すぐお問い合わせください。