クイックスペック

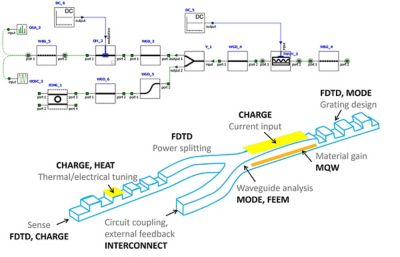

Ansys Lumerical INTERCONNECTは高速、正確、スケーラブルなフォトニックIC開発を可能にするために、Ansys Lumerical CML Compiler、Ansysマルチフィジックスソルバー、およびサードパーティのEDAおよびレイアウトツールベンダーとシームレスに連携します。

Ansysは次世代の技術者を支援します

学生は、世界クラスのシミュレーションソフトウェアに無料でアクセスできます。

未来をデザインする

Ansysに接続して、シミュレーションが次のブレークスルーにどのように貢献できるかを確認してください。

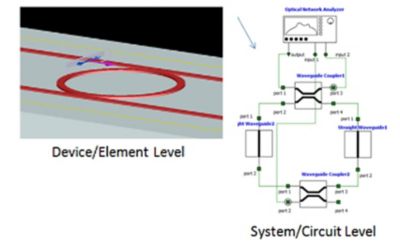

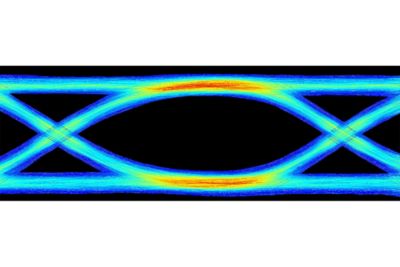

Ansys Lumerical INTERCONNECTは、古典的なフォトニック集積回路および量子フォトニック集積回路をシミュレーションしながら、複数のEDAプラットフォーム上でフォトニック回路と電子回路のコデザインとコシミュレーションを可能にします。

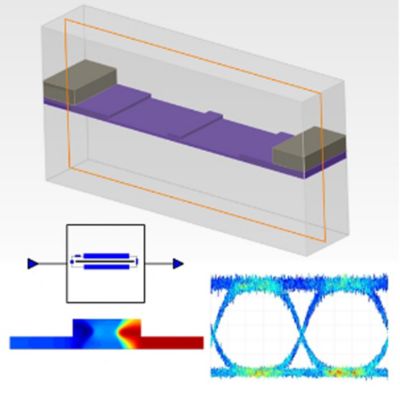

INTERCONNECTは、従来型のフォトニック集積回路(PIC)と量子PICの包括的な設計環境を提供します。業界でクラス最高の電子-フォトニックコデザイン、コシミュレーション機能、SDL、LVS、DRCなどの必須の設計ワークフローを備え、複数のEDAプラットフォームとの互換性があります。設計者はLumericalのPDK駆動プラットフォームを活用して、関連するエレクトロニクス、パッケージング、リンクを考慮し、製造およびカスタマイズが可能なフォトニック設計を効率的に作成できます。

Ansys Opticsにぜひご参加ください

Ansys Lumerical INTERCONNECTは高速、正確、スケーラブルなフォトニックIC開発を可能にするために、Ansys Lumerical CML Compiler、Ansysマルチフィジックスソルバー、およびサードパーティのEDAおよびレイアウトツールベンダーとシームレスに連携します。

2026年3月

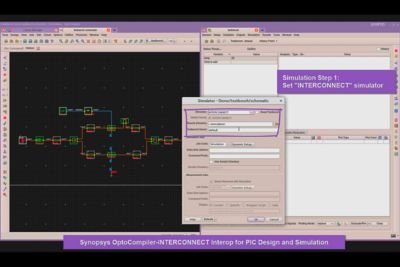

2026 R1リリースのAnsys Lumerical INTERCONNECTでは、シームレスなPyLumericalの自動化、Synopsys OptoCompilerとの相互運用性、メモリ使用量の削減による高速シミュレーションが可能となり、複雑な光集積回路の設計や高度な用途において信頼性の高いシミュレーション結果を提供します。

Synopsys OptoCompilerのユーザーは、Synopsys PrimeWaveで光集積回路シミュレータとしてLumerical INTERCONNECTソルバーを選択できるようになりました。 光集積回路の設計者は、OptoCompilerで回路図を作成し、INTERCONNECTコンパクトモデルライブラリに基づいてINTERCONNECT時間領域シミュレーションを実行できます。

PythonベースのソリューションであるPyLumericalを使用して、Lumericalツールをシームレスに自動化できます。PyAnsysエコシステムと完全に互換性があり、FDTD、MODE、マルチフィジックス、INTERCONNECT、さらにはoptiSLangやSpeosなど、AnsysのツールやオープンソースのPythonライブラリと統合できます。この最新の効率的なアプローチにより、ワークフローを簡素化して、マルチフィジックスシミュレーションを強化できます。

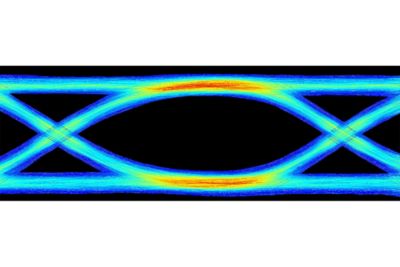

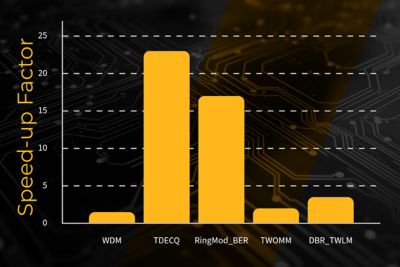

複雑で要求が高い回路であっても、高速化とメモリ使用量の削減によりシミュレーション性能を向上させることができます。WDMアーキテクチャ、TDECQ解析、リングモジュレータBERなどの高度な設計に最適で、相互接続された素子を効率的に処理するように設計されています。精度と一貫性を必要とする大規模な用途や長時間にわたるシミュレーション用に最適化されたツールを使用して、信頼性の高い結果を達成します。

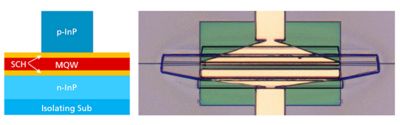

「お客様に比類のない設計の柔軟性と信頼性を提供するために、業界をリードするフォトニックシミュレーションツールのプロバイダーであるAnsys Lumericalを最初のSOAコンパクトモデルの開発におけるパートナーとして選びました」

「シリコンフォトニックおよびCMOSチップのコデザインとコシミュレーションのためにAnsysが提供する統合された電子-フォトニックワークフローは、設計プロセスの迅速化、エラーの少ない良好なチップの製造、市場投入までの時間の短縮に不可欠なツールです」

Ansys Lumerical INTERCONNECTは、古典的なフォトニック集積回路(PIC)と量子PICの包括的な設計環境を提供します。

電子集積回路およびPICのコデザインとコシミュレーションを実現する、業界で最も先進的で拡張性の高いプラットフォームを体験してください。

INTERCONNECTの広範なモデルライブラリ、すぐに使用できるファウンドリ校正モデル、またはカスタマイズされたコンパクトモデルを使用して、幅広い光集積回路を設計および最適化できます。

エンジニアの作業時間の34%はシミュレーションデータの検索に費やされています。このビデオでは、このような課題をAnsys Minervaで解決し、エンジニアの生産性を高める方法について説明します。

シミュレーションプロジェクトに伴う複雑さを軽減し、チームメンバーが協調して作業できるようにすることで、時間を節約し、プロジェクト全体で一貫したベストプラクティスを確実に実行できます。

Ansysは、障がいを持つユーザーを含め、あらゆるユーザーが当社製品にアクセスできることがきわめて重要であると考えています。この信念のもと、US Access Board(第508条)、Web Content Accessibility Guidelines(WCAG)、およびVoluntary Product Accessibility Template(VPAT)の最新フォーマットに基づくアクセシビリティ要件に準拠するよう努めています。

エンジニアリング課題に直面している場合は、当社のチームが支援します。豊富な経験と革新へのコミットメントを持つ当社に、ぜひご連絡ください。協力して、エンジニアリングの障害を成長と成功の機会に変えましょう。ぜひ今すぐお問い合わせください。