-

-

学生向け無料ソフトウェアにアクセス

Ansysは次世代の技術者を支援します

学生は、世界クラスのシミュレーションソフトウェアに無料でアクセスできます。

-

今すぐAnsysに接続!

未来をデザインする

Ansysに接続して、シミュレーションが次のブレークスルーにどのように貢献できるかを確認してください。

国および地域

無料トライアル

製品およびサービス

リソースとトレーニング

当社について

Back

製品およびサービス

抵抗と電流密度のチェックは、静電放電(ESD)の検証に有用で必要なステップですが、シミュレーションを設定する際には適切な注意を払う必要があります。標準的なポストレイアウトネットリストに使用する寄生成分抽出ツールでは、実際の値よりも最大で100倍高いまたは低い抵抗値が計算されることがあります。これは極めて大きな不一致ですが、電流密度についても同様の不一致が見られることがあります。こうした問題は、最新のサブ10nmテクノロジー(インターコネクト抵抗値が高いノード)で特に深刻です。このようなシミュレーションに頼ると、ESDの問題を見逃したり、適切なレイアウトで人為的誤差を修正するための時間が無駄になったりします。

幸いなことに、これらの不一致の原因は解明されているため、適切なシミュレーション手順を用いて簡単に修正できます。寄生成分の抽出やシミュレーションアーチファクトを回避するためには、デバイス上およびデバイス近傍の現実的な電流流れを模倣するシミュレーション条件を使用して再現する必要があることは明白ですが、これらの条件が満たされないこともあり、前述した誤差につながります。

このような誤差の最も一般的な根本原因は、次の2つです。

- 分散されたESDダイオードを単一インスタンスピンを持つセルとして誤って処理することで生じる人為的に高い抵抗値

- ESDダイオードとポートを小さな(1ミリオーム(mΩ))抵抗器で接続することで生じる人為的に低い抵抗値

ESDワークフローの概要

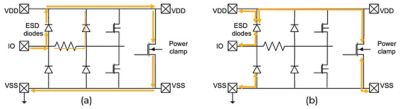

抵抗と電流密度のチェックは、ESD保護ネットワークを検証するためにポストレイアウトネットリストに対して実行されます(図1を参照)。1ポイントツーポイント(P2P)抵抗は、メタライゼーションの品質のプロキシ(性能指数)およびESD応力電圧のプロキシとして使用されます。P2P抵抗値が高い(1Ωを超える値など)場合は、メタライゼーションに関する問題が生じているため、デバッグや改善が必要となります。

図1: ESD保護ネットワークの(a)ESD電流経路と(b)P2P抵抗値(赤色の矢印)。パッドとESDダイオードの間の抵抗値、ダイオードと電源クランプの間の抵抗値、およびその他の抵抗値を計算して、ESD保護のロバスト性と品質を検証する。

近年、多くのファブレス半導体設計会社が、標準的な寄生成分抽出ツールで作成されたポストレイアウトネットリストを使用した場合に、ESD抵抗および電流密度シミュレーションで不可解な問題が生じると報告しています。これらの問題は、特にインターコネクト抵抗値が高い最新のサブ10nmノードで深刻になっています。

ESDダイオードとパッドまたは電源クランプ間の抵抗値が不当に高いまたは低い(最大で100倍)問題や、インターコネクト内で非物理的な電流密度が示される問題は、一般的には、ファブレス半導体設計会社がファウンドリから提供されるESDダイオードのパラメータ化されたセル(pセル)を使用する場合に発生します。これらのセルは、ファウンドリによって設計、検証、適格性評価されているため、問題がないはずですが、ESDセルと電源ネットあるいはIOネットの接続品質が適切でないことがあります。このように、接続品質が適切でない場合は、高い抵抗値や電流密度が示され、深刻なESD問題につながります。そのため、ESDセル自体の品質が高くても、ESDネットワーク全体での抵抗と電流密度のチェックが必要になります。

単一インスタンスピンによる人為的に高い抵抗値のケース

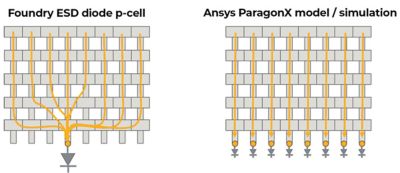

ファウンドリから提供されるプロセス設計キット(PDK)では、ESDダイオードは、一般的に陽極と陰極の各端子に単一のインスタンスピンを持つpセルとして表されます。これは、電源クランプの金属酸化膜半導体電界効果トランジスタ(MOSFET)が通常扱われる方法とは異なります。PDKでは、MOSFETは、マルチフィンガーデバイスの個々のフィンガーが独立したデバイスインスタンスとして表されます。また、端子として独自のインスタンスピンも含まれていますが、

これらは通常、ポイントツーポイント(P2P)抵抗シミュレーションの開始点または終了点として使用されます。その結果、ESDダイオードのpセルシミュレーションのケースでは、図2aに示すように、電流は単一の離散点に流れていき、人為的な電流集中、高電流密度値、高い広がり抵抗が生じます。

図2: ESDダイオードの垂直方向の断面図。(a)単一インスタンスピンを使用した場合と、(b)ダイオード領域全体で現実的な方法で電流が分散されるシミュレーションの電流流れのパターン。

これらの高い値は、単一の個別インスタンスピンによって広く分散されたデバイスの誤った表現によって引き起こされるシミュレーションのアーチファクトです。実際の動作では、ESDダイオードは全フィンガーに電流が伝導し、ESDの総電流は広い領域にほぼ一様に分散されます。

さらに、多層構成の高度なテクノロジーノードでは、下部の導体層が高いシート抵抗率を持ちます。これらは垂直電流の配線に使用され、全抵抗にほとんど寄与しません。能動素子の上の接触およびビアは、垂直電流を並列に(理想的には一様に)伝導させます。電流は多数の接触とビアで共有されるため、全抵抗は低くなります。

反対に、単一インスタンスピンを開始点または終了点として使用するシミュレーションでは、電流はそのインスタンスピンの近くに集中します。その結果、下部の導体層(M0、M1、M2など)の(垂直ではなく)水平方向の電流や、インスタンスピンに近いビアの高電流密度など、人為的で非現実的な電流パターンが生じます。

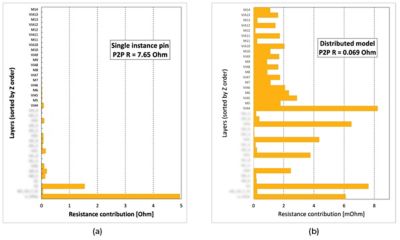

こうした振る舞いが、人為的に高い分散抵抗につながります。図3は、5nmテクノロジーの標準的なESDダイオードのシミュレーション結果を比較したものです。単一インスタンスピンを使用して計算された抵抗は、最大7.65Ωです。デバイス領域全体で現実的に分散された電流分布を示す条件を使用してシミュレーションした抵抗値は0.069Ωであり、これは100倍以上低い値となります。

さらに、問題の原因となっている層を特定しようとすると、これら2つのシミュレーション条件では、P2P全抵抗に対する層の寄与のランキングが異なることが報告されています。単一の個別インスタンスピンを使用したシミュレーションは、誤った層に焦点があたり、完全に誤った層の最適化につながる可能性があります。

図3: ESDダイオードからグランドネットポートへのP2P抵抗と、(a)単一インスタンスピンのケースおよび(b)分散されたシミュレーション条件の層ごとの抵抗寄与

下部層の電流密度分布も、図4に示すように、単一インスタンスピンの近くに強い電流集中が示されています。分散された電流流れの場合(図4b)、電流密度はほぼ一様で、ピーク値は単一インスタンスピンのケースの最大63倍低くなります。

図4: (a)単一インスタンスピンおよび(b)分散されたシミュレーション条件における電流密度分布。左のケース(a)のピーク電流密度は、右のケース(b)の63倍ほど高い。

人為的に低い抵抗値のケース

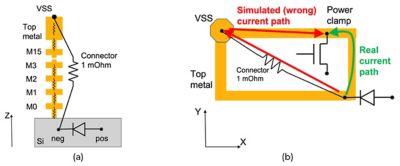

状況によっては、ESDダイオードのインスタンスピンが下部層に接続されず(拡散や接触など)、上部導体層にある電源ネットのポート(ピン)に直接接続されることがあります。このコネクタ抵抗器の抵抗値は、最小1mΩなど、非常に低い値になります。この誤った接続が発生するのは、なぜでしょうか。1つの可能性としては、寄生成分抽出ツールで、ESDダイオードの端子が抵抗値用に抽出されていないウェルまたは基板層にマッピングされていることです。その結果、寄生成分抽出ツールでは、コネクタ抵抗器によってポートとなる、任意点におけるネットのRネットワークに接続されます。これは、MOSFETのバルク端子が一般的にはポートに接続されるのと似ています(ウェルや基板が抵抗用に抽出されないため)。

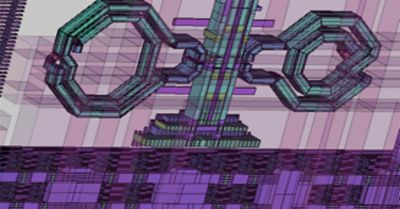

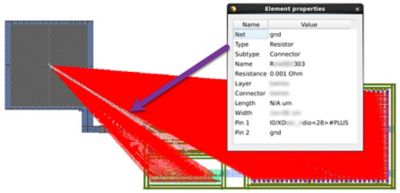

図5に示すように、寄生成分とそのプローブ結果を可視化することで、エンジニアは抽出の詳細を特定し、寄生成分抽出と電気解析で何が起こっているかを理解できるようになります。このような解析は、誤った接続を回避するのに役立ちます。

図5: レイアウト全体の寄生成分を可視化することで、接続性、非物理的なコネクタ抵抗器、プローブ寄生成分を特定できる。

つまり、ESDダイオードと電源ネットの接続性は設計上の誤りです。ESDダイオードから電源ネットのポートへの抵抗値は、このコネクタ抵抗器がインターコネクトを通過する実際の電流経路をバイパスするため、非常に低くなります(1mΩ)。

図6: (a)ESDダイオードのインスタンスピンを電源ネットポートに接続するコネクタ抵抗器の概略図と、(b)ESDダイオードから電源クランプ(緑色で表示)までの実際のESD電流経路と人為的にシミュレーションされた電流経路の上面図

同様に、図6に示すように、ESDダイオードから電源クランプへのシミュレーションされた電流経路は、実際の電流経路とは異なります。電流は、ESDダイオードから電源ネットポートまでの最小抵抗(最小電力損失)の経路をたどり、(低い抵抗値の)上部導体に沿って電源クランプに流れます。したがって、シミュレーションされた抵抗と電流密度は不正確であり、実際の抵抗と電流密度を表すものではありません。

このケースで抵抗と電流を適切にシミュレーションするには、コネクタの抵抗を取り除き、分散されるように、ダイオードのインスタンスピンを最下層に接続する必要があります。このプロセスは、寄生成分抽出ツールで行うのが最適です。

コネクタ抵抗器

コネクタ抵抗器は、寄生成分抽出ツールで部分的に隠されている機能です。これらは、レイアウト形状とその抵抗率によって生成されていない(つまり、非物理的な)抵抗器です。ユーザーがこれらの抵抗器を制御することはできません。抽出ツールのベンダーは、この機能に関する情報を半導体企業に公開していませんが、それは実装の内部詳細として見なしているためと考えられます。

コネクタ抵抗器は、さまざまな接続用途に使用されます。たとえば、デバイスのインスタンスピンを抵抗回路や他のインスタンスピンに接続するため、ネットの接続されていない(オープンな)部品を接続するため、短絡ポートに接続するためなど、さまざまな用途があります。それらの値は、0.1、1、10、または100mΩなど、一般的には非常に低い値です。ほとんどの場合、電気シミュレーションの結果に悪影響を及ぼすことはありません。しかし、前述のように、インターコネクトの有限抵抗を短絡したり、はるかに低い抵抗値を持つシステムに0.1Ωの抵抗を追加したりするなど、不可解な影響を示す、あるいは有害な影響をもたらすことがあります(たとえば、パワーFETはmΩの範囲のインターコネクト抵抗値を持つ)。

図5に示すように、レイアウト上のコネクタ抵抗器を理解、特定、可視化して、その存在と潜在的な影響を認識できることは、ポストレイアウトネットリストの構造、接続性、潜在的な落とし穴を十分に理解する上で重要です。寄生成分抽出シミュレーションを導入することで、このような理解を得られるようになります。

P2P抵抗および電流密度の詳細

適切な寄生成分抽出シミュレーションツールを使用して、ESDネットワークシミュレーションで不可解なP2P抵抗および電流密度の振る舞いを修正できる簡単なソリューションがあります。そうしたツールの1つが、ICレイアウト寄生解析およびデバッグソフトウェアであるAnsys ParagonXです。このブログでご紹介したすべてのシミュレーションと可視化は、Ansys ParagonXで実行されたものです。ESD回路設計で正しい抵抗値と電流密度値を達成し、大きな誤差を回避するために、ParagonXがどのように役立つかについての詳細は、こちらのWebページをご覧ください。

参考文献

『ESD Electronic Design Automation Checks』 Technical report, ESD Association, 2014.無料ダウンロードはこちら: https://www.esda.org/zh_CN/store/standards/product/4/esd-tr18-0-01-14

Advantageブログ

Ansys Advantageブログでは、専門家が投稿した記事を公開しています。Ansysのシミュレーションが未来のテクノロジーにつながるイノベーションをどのように推進しているかについて最新の情報をご覧ください。