電阻與電流密度檢查是靜電放電 (ESD) 驗證中實用且必要的步驟,但在設定模擬時必須特別謹慎。針對標準佈局後網表的寄生萃取工具有時會算出比實際數值高出或低至 100 倍的電阻,這是非常巨大的差異。電流密度也可能會有顯著的偏差。這些問題在最新的次 10-nm 技術節點中尤其嚴重,這類節點具有相當高的互連電阻。依賴這類模擬結果,可能導致會錯過 ESD 問題,或者浪費時間試圖修正一個良好的佈局中的虛假錯誤。

所幸我們已經瞭解這些誤差的成因,且可以利用適當的模擬程序輕鬆修正。雖然模擬條件應該模擬並重現元件上及其附近的實際電流,以避免寄生萃取與模擬產生的假象,這一點看似理所當然,但有時卻因為未能滿足這些條件,而導致上述錯誤的發生。

這些錯誤最常見的兩個根本原因是:

- 將分散式 ESD 二極體錯誤地視為具有單一物件引腳的單元,會導致電阻值被人為地高估

- 用極小的電阻器 (1毫歐,或 mΩ) 將 ESD 二極體連接到埠上,會導致電阻值被人為地低估

ESD 工作流程概覽

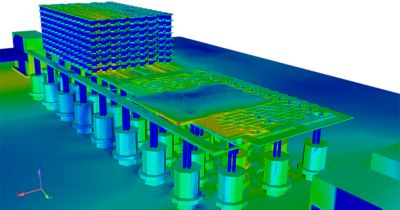

通常會在佈局後網表上進行電阻檢查與電流密度檢查,以驗證 ESD 保護網路 (見圖1)。1 點對點 (P2P) 電阻作為金屬化品質的性能指標,也作為 ESD 應力電壓的替代指標。較高的 P2P 電阻值 (例如超過 1 Ω) 表示金屬化存在問題,應對其進行除錯與改善。

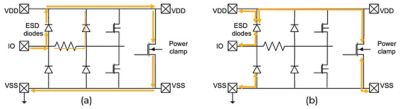

圖 1.(a) ESD 電流路徑,以及 (b) ESD 保護網路中的 P2P 電阻 (紅色箭頭)。計算焊盤與 ESD 二極體之間的電阻、二極體至電源箝制的電阻,以及其他電阻,來驗證 ESD 保護的穩健性與品質。

近年來,許多無晶圓廠半導體設計公司在使用標準寄生萃取工具產生的佈局後網表時,曾回報在ESD 電阻與電流密度模擬方面出現令人困惑的問題。這些問題在最新的次 10-nm 節點中變得尤其嚴重,這類節點具有相當高的互連電阻。

當無晶圓廠半導體設計公司使用晶圓代工廠提供的 ESD 二極體參數化單元 (p 單元) 時,通常會發生 ESD 二極體與焊盤或電源箝制之間電阻值異常地高或低 (相差約 100倍),以及互連中出現非物理性的電流密度等問題。這些單元由晶圓代工廠設計、驗證並認證,理論上品質應該良好。然而,這些 ESD 單元與電源網路或 IO 網路之間的連接品質可能很差。這類劣質連接會導致高電阻與高電流密度,進而造成嚴重的 ESD 問題。因此,即使 ESD 單元本身品質優良,仍需要對整個 ESD 網路進行電阻與電流密度檢查。

由單一物件引腳導致的虛假高電阻情況

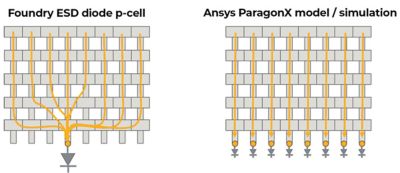

在晶圓代工廠提供的製程設計套件 (PDK) 中,ESD 二極體通常呈現為每個端子 (陽極與陰極) 僅有單一物件引腳的 p 單元。這與 PDK 中對電源箝制金氧半導體場效電晶體 (MOSFET) 的通常處理方式不同,在 PDK 中,多指元件的每個指狀單元都會呈現為獨立元件物件,並擁有端子的各自物件引腳。

這些物件引腳通常會用作點對點 (P2P) 電阻模擬的起源或目的地。因此,在 ESD 二極體 p 單元模擬中,電流會流入單一的離散點,造成虛假的電流擁擠、高電流密度值,以及高擴散電阻,如圖 2a 所示。

圖 2.ESD 二極體的垂直剖面圖,顯示使用 (a) 單一物件引腳與 (b) 在二極體區域內以實際方式分布電流時的模擬電流流動模式

這些高數值是模擬中的假象,其起因是錯誤地以單一離散物件引腳表示大型分散式元件。在實際運作中,ESD 二極體會透過所有指狀單元傳導電流,且整體 ESD 電流會大致均勻地分布於較大範圍。

此外,在具有多個層的先進製程節點中,底部金屬層具有較高的片電阻。這些金屬層會用於垂直電流佈線,對總體電阻貢獻很小。位於主動元件之上的觸點與通孔會平行傳導垂直電流,理想情況下為均勻分佈。電流由多個接點與通孔分擔,導致總電阻較低。

相反地,在使用單一物件引腳作為起點或終點的模擬中,電流會集中並擠在該物件引腳附近。這會造成不真實的電流流動模式,例如底部金屬層 (M0、M1、M2 等) 出現橫向 (而非垂直) 電流、通孔中的電流分佈極度不均,以及靠近物件引腳的通孔出現高電流密度。

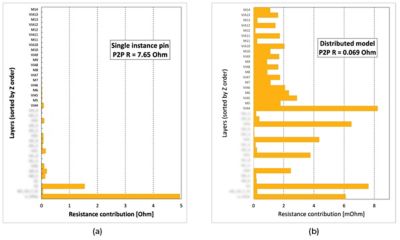

這樣的現象會導致虛高的擴散電阻。圖 3 比較了 5-nm 技術下標準 ESD 二極體的模擬結果。使用單一物件引腳所計算出的電阻約為 7.65 歐姆。在採用較為真實的 (分散式) 電流分佈條件進行模擬所得的電阻為 0.069 歐姆,比前者低了超過 100 倍。

此外,在嘗試判斷哪些金屬層造成問題時,這兩種模擬條件回報各層對 P2P 總電阻時的貢獻排序也不同。使用單一離散物件引腳的模擬可能會因其關注錯誤的層,而出現完全錯誤的層最佳化策略。

圖 3.ESD 二極體到接地網路埠的 P2P 電阻,以及 (a) 單一物件引腳情況與 (b) 分散式模擬條件下各層的電阻貢獻

如圖 4 所示,底部金屬層中的電流密度分佈也顯示出在單一物件引腳附近發生明顯的電流擁擠現象。在分散式電流流動的情況下 (圖 4b),電流密度大致均勻,且其峰值大約比在單一物件引腳的情況低了 63 倍。

圖 4.(a) 單一物件引腳與 (b) 分散式模擬條件下的電流密度分佈。左邊案例 (a) 的電流密度峰值比右邊案例 (b) 高出 63 倍。

虛假低電阻的情況

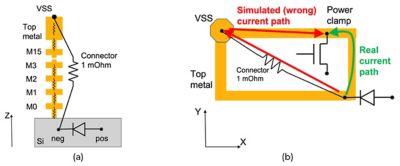

在某些情況下,ESD 二極體的物件引腳不是連接到低部金屬層 (例如擴散層或接點),而是直接連接到位於頂部金屬層的電源網路埠 (引腳) 上。這種連接電阻器的電阻非常低,可能為 1 mΩ。為什麼會發生這種錯置連接?其中一個可能原因是,ESD 二極體的端子對應到井層或基板層,而寄生萃取軟體並未萃取這些層的電阻。因此,寄生萃取工具會將該端點透過一個連接電阻器,隨意地接到該網路的某個電阻網路節點上,而該節點往往是某個埠。這與 MOSFET 的整體端子通常會連接到埠的情況類似 (因為井層與基板層通常不萃取電阻)。

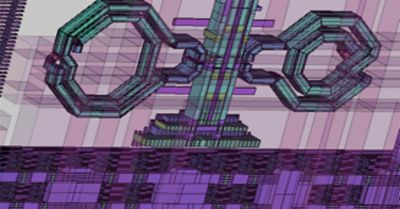

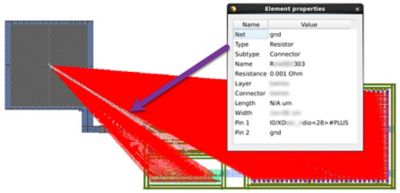

如圖 5 所示,藉由將寄生效應視覺化並對其進行探查,工程師可以辨識出這類擷取細節,並瞭解寄生萃取與電力分析的實際狀況。這類分析有助於避免錯置連接的情況發生。

圖 5.將佈局上的寄生效應視覺化,這有助於辨識連線、非物理性連接電阻器,以及寄生效應探查

因此,ESD 二極體與電源網路的連接是種設計錯誤。由於此連接電阻器通過互連並規避了實際的電流路徑,導致 ESD 二極體到電源網路埠的電阻非常低 (1 mΩ)。

圖 6.(a) 連接電阻器將 ESD 二極體物件引腳與電源網路埠連結的示意圖,與 (b) 自 ESD 二極體到電源箝制的實際 ESD 電流路徑 (以綠色顯示) 與人工模擬之電流路徑的俯視圖

同樣地,如圖 6 所示,從 ESD 二極體到電源箝制的模擬電流路徑與實際電流路徑並不相同。電流會從 ESD 二極體經由最小電阻 (即最小電力消耗) 的路徑流向電源網路埠,然後沿著 (低電阻的) 頂部金屬層往下流向電源箝制。因此,模擬得出的電阻與電流密度都不正確,無法反映實際的電阻與電流密度情況。

要正確針對此情況模擬電阻與電流,就必須移除連接電阻,並將二極體的物件引腳以分散式方式連接至最低金屬層。這應由寄生萃取工具來完成最為理想。

連接電阻器

連接電阻器是寄生萃取工具中的半隱藏功能。這些是非物理性電阻器,也就是說,它們不是由佈局形狀及其電阻率所產生的。這些電阻器無法由使用者控制。萃取工具的廠商通常不會讓半導體公司瞭解這項功能,可能是因為它被視為實作上的內部細節。

連接電阻器可用於多種連接目的—例如,將元件的物件引腳連接到電阻網路或其他物件引腳、連接網路上中斷連接 (「開路」) 的部分、讓埠「短路」,以及其他各種用途。這些電阻的值通常非常低,例如 0.1、1、10 或 100 mΩ。大多數情況下,它們對電子模擬結果並無有害影響。然而,如上所述,有時它們會造成奇怪或有害的影響,例如讓互連的有限電阻短路,或將 0.1 Ω 的電阻新增至原本電阻更低的系統 (例如功率 FET,其互連電阻值落在 mΩ)。

能夠理解、辨識並在佈局上視覺化連接電阻器 (如圖5所示),並意識到它們的存在與可能造成的影響,對於深入瞭解佈局後網表的結構、連接與潛在問題非常重要。寄生萃取模擬可以為您提供這種程度的理解。

深入瞭解 P2P 電阻與電流密度

很明顯地,若使用合適的寄生萃取模擬工具,就可以利用簡單的解決方案來修正 ESD 網路模擬中異常的 P2P 電阻與電流密度異常。此處介紹的所有模擬與視覺化操作均使用了 Ansys ParagonX 積體電路佈局寄生分析和除錯軟體這項工具。請造訪該網頁以深入瞭解 ParagonX 軟體如何協助您在 ESD 電路設計中獲得正確的電阻與電流密度數值,並避免遇到部分半導體設計人員所經歷的巨大誤差。

參考資料

「ESD 電子設計自動化檢查」,技術報告,ESD 協會,2014 年。免費下載:https://www.esda.org/zh_CN/store/standards/product/4/esd-tr18-0-01-14