电阻和电流密度检查是静电放电(ESD)验证时的必要步骤,但在设置仿真时必须谨慎,以确保获得准确可靠的结果。标准版图后网表上的寄生提取工具有时会计算得到比实际值高或低至最多100倍的电阻,这不仅造成了巨大偏差,还会显著降低电流密度。这些问题在最新的亚10nm技术(即具有高互连电阻的节点)中尤为凸显。如果依靠此类仿真,要么会导致遗漏ESD问题,要么需要浪费时间去修复良好版图上的人为错误。

幸运的是,使用正确的仿真程序,可以了解造成这些偏差的原因并且轻松对其纠正。显而易见,仿真条件应该能够模拟和再现设备中和设备附近的真实电流,以避免寄生提取和仿真伪影,但有时无法满足这些条件,就会导致上述误差。

导致此类误差的两个最常见的根本原因是:

- 将分布式ESD二极管错误地处理为具有单个实例引脚的单元,从而人为地导致电阻值较高

- 用一个小电阻(1 mΩ)将ESD二极管与端口连接,从而人为地导致电阻值较低

ESD工作流程概述

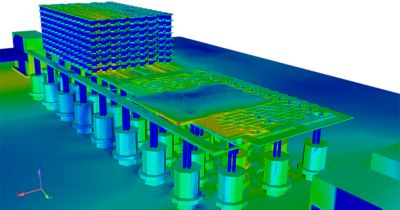

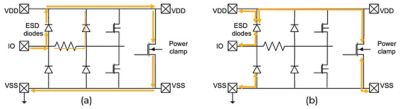

电阻检查和电流密度检查通常在版图后网表上进行,以验证ESD保护网络(参见图1)。1点对点(P2P)电阻既可用作金属化质量的指标,也可用作ESD应力电压的指标。P2P电阻值较高(例如高于1 Ω)表示金属化存在问题,应进行调试和改进。

图1:(a)ESD电流路径和(b)ESD保护网络中的P2P电阻(红色箭头)。计算焊盘和ESD二极管之间的电阻、二极管到电源钳的电阻以及其他电阻,以验证ESD保护的稳健性和质量。

近年来,据许多无晶圆厂半导体设计公司的报告称,在使用标准寄生提取工具生成的版图后网表时,ESD电阻和电流密度仿真存在令人困惑的问题,并且这些问题在具有高互连电阻的最新亚10nm节点中尤为凸显。

在无晶圆厂半导体设计公司使用代工厂提供的ESD二极管参数化单元/版图单元(p-cell)时,通常会出现ESD二极管和焊盘或电源钳之间的电阻过高或过低(~100倍)的情况,以及互连中存在非物理的电流密度等问题。这些单元由代工厂进行设计、验证和认证,应该具有良好的质量。然而,ESD单元到电源网络和IO网络的连接质量可能很差。这种不良连接会导致高电阻和高电流密度,从而导致严重的ESD问题。这也正好解释了,为什么即使ESD单元本身具有高质量,也需要对整个ESD网络进行电阻和电流密度检查。

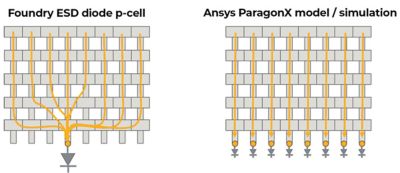

由单个实例引脚引起的人为高电阻情况

在代工厂提供的工艺设计套件(PDK)中,ESD二极管通常表示为p-cell,每个端子(阳极和阴极)都有单个实例引脚。这与PDK对电源钳金属氧化物半导体场效应晶体管(MOSFET)的常见处理方式有所不同,其中,多触点器件的每个单独触点都被表示为单独的器件实例,并具有自己的端子实例引脚。

这些实例引脚通常用作点对点(P2P)电阻仿真的起点或目标点。因此,在ESD二极管p-cell仿真中,电流流入单个离散点,从而产生人为的电流拥挤效应、高电流密度值和高扩散电阻,如图2a所示。

图2:ESD二极管的垂直横截面,显示了使用(a)单个实例引脚和(b)以逼真的方式在二极管区域上分配电流的仿真电流流动模式

这些较高的值是仿真的伪影,它是由使用单个离散实例引脚来错误表示大型分布式器件而引起的。在实际操作中,ESD二极管通过所有触点传导电流,总的ESD电流基本上均匀地分布在较大的区域上。

此外,在具有许多层的先进技术节点中,下层金属层具有较高的片层电阻率。它们可用于垂直电流布线,并且对总电阻的影响很小。在理想情况下,有源器件上方的触点和通孔能够以一种均匀的方式、并行传导垂直电流。该电流由许多触点和通孔共同分担,从而产生较低的总电阻。

相反,在使用单个实例引脚作为起点或目标点的仿真中,电流会集中聚集在该实例引脚附近。这会导致人为的、不符合实际的电流流动模式,例如下层金属层(M0、M1、M2等)中的横向(而非垂直)电流,以及通孔中高度不均匀的电流和靠近实例引脚的通孔中的高电流密度。

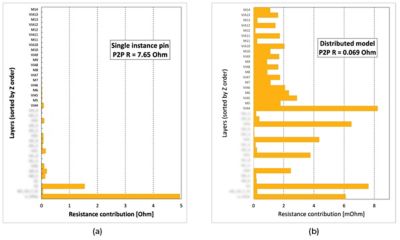

然后,上述行为又会导致人为的高扩散阻力。图3比较了5nm技术的标准ESD二极管的仿真结果。使用单个实例引脚计算出的电阻为~7.65 Ω,而在器件区域上提供真实(分布式)电流分布的条件下仿真的电阻为0.069 Ω,比之前的值低100倍以上。

此外,在试图确定是哪些层导致问题时,这两种仿真条件对于各层对P2P电阻贡献的排序是不同的。使用单个离散实例引脚进行仿真,可能由于聚焦错误的层,而导致制定完全错误的层优化策略。

图3:(a)单个实例引脚案例和(b)分布式仿真条件下的ESD二极管到接地网络端口的P2P电阻以及逐层电阻分布

下层金属层的电流密度分布还显示单个实例引脚附近存在强烈的电流拥挤,如图4所示。在分布式电流(图4b)情况下,电流密度基本上是均匀的,其峰值比单个实例引脚的情况低~63倍。

图4:(a)单个实例引脚和(b)分布式仿真条件下的电流密度分布。左侧案例(a)的峰值电流密度比右侧案例(b)的高63倍。

人为低电阻案例

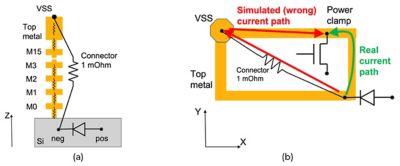

在某些情况下,ESD二极管实例引脚不是连接到下层金属层(如扩散层或接触层),而是直接连接到位于最上层金属层的电源网络端口(引脚)。这种连接电阻的电阻非常低,例如1 mΩ。为什么会出现这种错误的连接?一种可能性是ESD二极管的端子被映射到一个阱层或衬底层,而寄生参数提取软件不会对这些层提取电阻值。因此,寄生提取工具通过连接电阻,将其连接到某个网络的R网络中,而连接的位置比较随机,结果实际上连接到了该网络的端口。这与MOSFET的体端子连接到端口的常用方式类似(因为不会提取阱层和衬底层的电阻)。

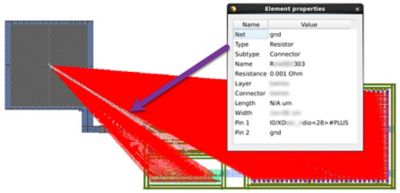

寄生效应的可视化及探测使工程师能够识别此类提取细节,并了解寄生提取和电气分析中的情况,如图5所示。此类分析可以帮助他们避免错误布局的连接。

图5:在版图上实现寄生效应的可视化,有助于识别连接和非物理连接电阻,以及探测寄生效应

因此,ESD二极管与电源网络的连接是一个设计错误。ESD二极管到电源网络端口的电阻非常低(1 mΩ),因为该连接电阻绕过了流经互连的实际电流路径。

图6:(a)将ESD二极管实例引脚与电源网络端口连接的连接电阻的示意图;(b)从ESD二极管到电源钳的真实ESD电流路径(显示为绿色)与人工仿真电流路径的顶视图

同样地,从ESD二极管到电源钳的仿真电流路径也不同于实际电流路径,如图6所示。电流会流经从ESD二极管到电源网络端口的最小电阻(最小耗散功率)路径,然后沿(低电阻)顶部金属流向电源钳。因此,仿真的电阻和电流密度不是正确的,并不代表实际的电阻和电流密度。

为了对这种情况下的电阻和电流进行正确仿真,必须删除连接电阻,并且二极管的实例引脚应以分布式方式连接到最低层。最好使用寄生提取工具来完成此操作。

连接电阻

连接电阻是寄生提取工具中的半隐藏特性。它们属于非物理电阻,即它们不是由版图形状及其电阻率产生的,而且无法由用户进行控制。提取工具供应商不会向半导体公司宣传此特性,这可能是因为它被视为一种实施过程中的内部细节。

连接电阻可用于各种连接目的,例如,将器件的实例引脚连接到电阻网络或其他实例引脚;连接到网络中断开连接的(“开路”)部分;连接到“短路”端口;以及用于许多其他目的。它们的电阻值通常非常低,例如0.1 mΩ、1 mΩ、10 mΩ或100 mΩ,因此在大多数情况下不会对电气仿真结果产生不利影响。然而,如前所述,它们有时会产生异常或有害的影响,例如使互连的有限电阻短路,或向电阻低得多的系统(例如,电源FET的互连电阻值在mΩ的范围内)增加0.1 Ω的电阻。

很重要的一点是了解、识别和可视化版图上的连接电阻(如图5所示),并了解其存在及潜在影响,这有助于了解版图后网表中的结构、连接和潜在缺陷。寄生提取仿真可以在这个方面为您提供帮助。

进一步了解P2P电阻和电流密度

显然,使用适当的寄生提取仿真工具,可以轻松地在ESD网络仿真中纠正异常的P2P电阻和电流密度情况。Ansys ParagonX集成电路版图寄生分析和调试软件,便是这类仿真工具之一,可用于进行本文介绍的所有相关方面的仿真和可视化。欢迎访问该网页,详细了解ParagonX软件如何帮助您在ESD电路设计中获得正确的电阻和电流密度值,并帮助半导体设计人员避免较大误差。

参考资料

“ESD Electronic Design Automation Checks,” Technical report, ESD Association, 2014.免费下载:https://www.esda.org/zh_CN/store/standards/product/4/esd-tr18-0-01-14

Advantage博客

Ansys Advantage博客(The Advantage Blog)由Ansys专家和其他技术专家撰写,让您随时了解Ansys如何为创新赋能,推动人类踏上伟大征程。