-

-

学生向け無料ソフトウェアにアクセス

Ansysは次世代の技術者を支援します

学生は、世界クラスのシミュレーションソフトウェアに無料でアクセスできます。

-

今すぐAnsysに接続!

未来をデザインする

Ansysに接続して、シミュレーションが次のブレークスルーにどのように貢献できるかを確認してください。

国および地域

無料トライアル

製品およびサービス

リソースとトレーニング

当社について

Back

製品およびサービス

Over the past few years, chip designs have been getting larger, with compute workloads exceeding billions of nodes. This has been accelerated, pun intended, by the advent of artificial intelligence and machine learning. A recent chip shown at a corporate event looked more like a printed circuit board!

For these designs, it is important that the chip power model (CPM) be generated quickly and accurately. This has a direct impact on reducing the time taken for chip-package co-simulation and therefore the time for entire design cycle. Now, Ansys has revolutionized chip-package-system power integrity analysis with Chip Power Model-SC (CPM-SC). Internal tests show that this innovation slashes the model generation runtimes by an astonishing 20X, particularly for complex and large-scale 3D-IC designs, setting a new standard in efficiency and performance.

What is Chip Power Model?

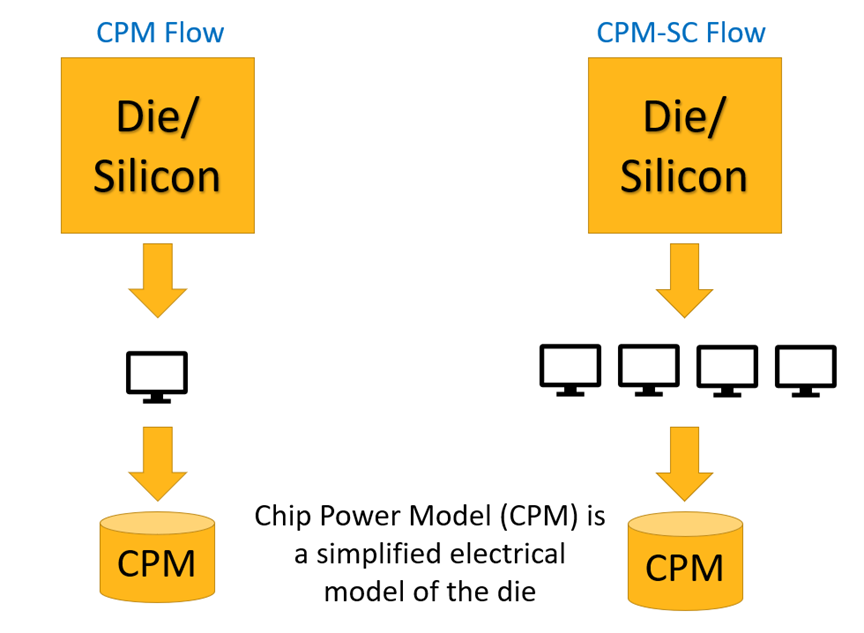

Power integrity simulations for design closure need to run a chip-package (and board) co-simulation. Running this system level simulation with the full die model is extremely slow and perhaps an overkill. To address this need to simplify the die model for co-simulation needs, Ansys proposed a simplified model in the form of CPM. CPM is a SPICE-accurate model of the chip’s power delivery network (PDN) over a broad band frequency. As compared to the early efforts of using a lumped resistance and capacitance model for the die, the CPM presented an effective way to include the die model for system-level simulations. CPM captured all the relevant parasitics in the die model from DC to the Gigahertz range. This enabled designers to perform accurate system-level predictive power delivery network simulations with high confidence in the results.

The comparison between the classic CPM model generation and the new CPM-SC model generation showing distributed compute for the latter, resulting in runtime improvement and higher capacity.

Why Do We Need CPM-SC?

When simplifying a large die with billions of nodes into a CPM model, the primary challenge is to preserve the impedance information of the original die across multiple port pairs over a broad range of frequencies while distributing the problem over multiple workers with a smaller memory footprint. In addition, when designs have additional components like MIMCap (metal insulator metal capacitor), it becomes even more challenging to capture the combined behavior of the die. To solve this problem, which is exacerbated by the simultaneous increase in 3D-IC designs, Ansys has come up with algorithmic innovations in combination with state-of-the art distributed computing to deliver the CPM-SC model.

What Are the Benefits of CPM-SC?

CPM-SC leverages the Ansys SeaScape elastic compute platform, thus enabling orders of magnitude faster runtime and reduction in memory consumption while maintaining accuracy. In experiments done internally, the results show on average 20X improvement in runtime and 15X reduction in memory consumption for CPM-SC when compared to CPM. While improvement is seen for all designs, CPM-SC is a necessity for larger designs (>1 billion nodes) to produce simplified models.

The Ansys Chip Power Model-SC speeds up runtime and lowers memory consumption, which is especially evident in large designs with more than 1 billion nodes.

Ansys' CPM-SC model offers unprecedented speed and efficiency. By leveraging advanced algorithms and distributed computing, CPM-SC ensures accurate and rapid generation of simplified models, making it indispensable for the future of large-scale and/or 3D-IC power integrity analysis.

Learn more about Ansys semiconductor products, and contact us for more information on Ansys CPM-SC model.

The Advantage Blog

The Ansys Advantage blog, featuring contributions from Ansys and other technology experts, keeps you updated on how Ansys simulation is powering innovation that drives human advancement.