アプリケーション

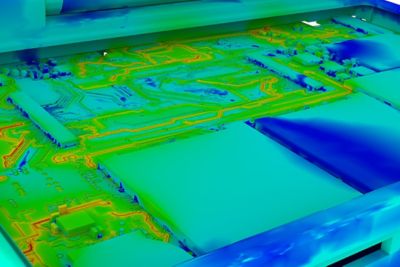

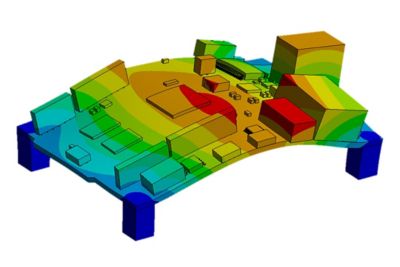

ハイテクエレクトロニクスシステムは、モビリティからエネルギー、第4次産業革命、インシリコヘルスケアまで、さまざまな業界で発生する破壊的な変革のバックボーンです。Ansysは、半導体設計および製造におけるシリコンの規模から、パッケージやシステムにおける熱的信頼性および電子部品の信頼性、都市などの電気的に規模が大きな環境に至るまで、ハイテクエレクトロニクス向けのシミュレーションアプリケーションを提供します。

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

Ansysは、シミュレーションエンジニアリングソフトウェアを学生に無償で提供することで、未来を拓く学生たちの助けとなることを目指しています。

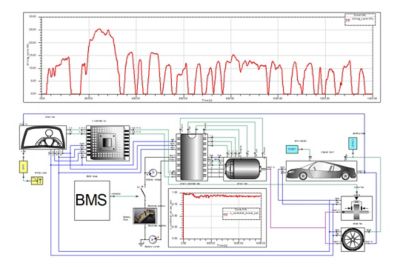

インテリジェントコネクティビティにより、自動運転車からインダストリアルIoTまで、私たちの世界は見違えるほど変化しつつあります。これらのテクノロジーを実現するには、シミュレーションが不可欠です。

5G、自動運転車、スマート製品、スマート住居、スマートシティ、そしてスマート工場が現実のものになるためには、それを可能にするエレクトロニクステクノロジーで、これまでにないレベルの信頼性をもたらす必要があります。無数のセンサー、マイクロプロセッサ、通信コンポーネントを使用することで、エンジニアは製品の信頼性と性能に関する大きな課題に直面しています。エンジニアリングシミュレーションは、ハイテク企業が目標とする性能、エネルギー効率、コスト、市場投入までの期間を達成し、それを上回る革新的で信頼性の高い製品を提供するのに重要な役割を果たします。

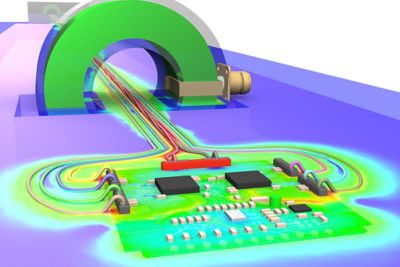

5Gとその先への競争に勝つ

サービス品質が重要な指標となる中で、エンジニアはミリ波設計からビームフォーミング、MIMO、シグナルおよびパワーインテグリティに至るまで、重大な課題に直面しています。Ansysの包括的なマルチフィジックスソリューションは、この競争に勝つ唯一の方法です。

デジタルトランスフォーメーション、AI/ML、IIoTをリード

今日のインテリジェント製品は、人工知能(AI)、センサー、通信技術を利用して、快適性、利便性、効率性を提供しています。シミュレーションにより、エンジニアは従来の設計の常識に挑戦し、不可能を可能にすることができます。

IIoTによるインテリジェンスと自動化の推進

マルチフィジックスシミュレーションソリューションは、IIoT時代において、信頼性が高く、高性能で、エネルギー効率の高いコンポーネントやシステムの開発を加速するために不可欠です。

エンジニアリングの生産性とイノベーション

ハイテク業界の企業は、生き残るために、迅速にイノベーションを起こす必要があります。シミュレーション主導のデジタルトランスフォーメーションにより、企業はより迅速に、より少ないコストとリソースでイノベーションを進めることができます。

ハイテクエレクトロニクスシステムは、モビリティからエネルギー、第4次産業革命、インシリコヘルスケアまで、さまざまな業界で発生する破壊的な変革のバックボーンです。Ansysは、半導体設計および製造におけるシリコンの規模から、パッケージやシステムにおける熱的信頼性および電子部品の信頼性、都市などの電気的に規模が大きな環境に至るまで、ハイテクエレクトロニクス向けのシミュレーションアプリケーションを提供します。

Lorem Ipsum has been the industry's standard dummy text ever since the 1500s, when an unknown printer took a galley of type and scrambled it to make a type specimen book. It has survived not only five centuries

このe-bookでは、新しい設計パラダイムを実現するために必要な5つの重要な機能を、実例を用いて紹介します。

消費者向けエレクトロニクス製品から自動車や軍事製品まで、多くの業界で、それぞれのニーズに合わせて最適化されたシステムオンチップ(SoC: System-on-Chip)集積回路の設計が始まっています。それと同時に、機器の設計者は、複数のチップを1つのパッケージに統合して、より完全で高性能なソリューションを作成しています。市場シェア争いの勝敗は、これらの世界が1つになる場所、つまり3D集積回路(3D-IC)によって決まります。

接続性、デジタル化、自動運転が普及するにつれて、産業間の境界はかつてないほどの速さで曖昧になりつつあります。グローバルテクノロジー市場が3兆ドル規模となることが見込まれているこの新たな競争の場は、システムエレクトロニクスと半導体の世界がぶつかる場所、すなわち3D ICシステムオンチップとなります。

Lorem Ipsum has been the industry's standard dummy text ever since the 1500s, when an unknown printer took a galley of type and scrambled it to make a type specimen book. It has survived not only five centuries

エンジニアリング課題に直面している場合は、当社のチームが支援します。豊富な経験と革新へのコミットメントを持つ当社に、ぜひご連絡ください。協力して、エンジニアリングの障害を成長と成功の機会に変えましょう。ぜひ今すぐお問い合わせください。