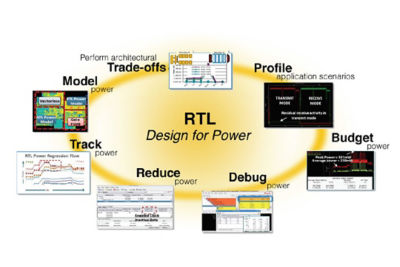

Power efficiency is a paramount consideration in semiconductor design. RTL designers working on applications from mobile and CPUs to networking and automotive ICs use Ansys PowerArtist to analyze and reduce power early in the development cycle for the highest impact. Compared to traditional gate-level methodologies, PowerArtist provides rapid turnaround on multimillion instance designs, and enables early power-related design decisions. PowerArtist’s consistently accurate technology not only analyzes but can also automatically identify reduction opportunities through the unique modeling of physical implementation effects.

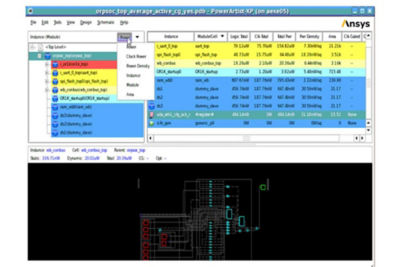

RTL designers - especially those new to power - can easily and efficiently debug power hotspots with PowerArtist’s GUI.

PowerArtist provides the industry’s fastest power profiling capability, which can analyze the activity of real applications comprising tens of milliseconds within hours — several orders of magnitude faster than traditional approaches. Efficient activity transfer interfaces with emulators enable fast streaming of millions of RTL activity cycles. New vector analytics score vectors for peak power coverage enabling designers to identify testbench deficiencies and enabling IR flows by ranking vectors for maximum coverage with minimum cycles.