簡要規格

PathFinder-SC 的整合式資料建模、擷取和暫態模擬引擎是 ESD 驗證的端到端解決方案。單次使用模式可讀取業界標準的設計格式、設定 ESD 規則、擷取電源網路的 RC, 並執行 ESD 模擬,以分析根本原因並提供修正與最佳化回饋,全都使用單一工具完成。

Ansys Pathfinder-SC 是高容量解決方案,可幫助您規劃、驗證和簽核 IP 及全晶片 SoC 設計,以確保完整性和抗靜電放電 (ESD) 的穩定性。

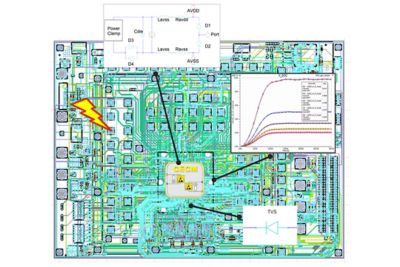

Ansys Pathfinder-SC 確認並隔離可能導致元件充電放電模式 (CDM)、人體靜電放電模式 (HDM) 或其他 ESD 事件發生晶片故障的設計問題的根本原因。它的高容量雲端原生架構可以利用數千個運算核心來快速的全晶片返回。PathFinder-SC 在 ESD 簽核時的電阻與電流密度檢視獲得主要晶圓代工廠的認證。

PathFinder-SC 的整合式資料建模、擷取和暫態模擬引擎是 ESD 驗證的端到端解決方案。單次使用模式可讀取業界標準的設計格式、設定 ESD 規則、擷取電源網路的 RC, 並執行 ESD 模擬,以分析根本原因並提供修正與最佳化回饋,全都使用單一工具完成。

靜電放電和電流密度是決定晶片真實世界穩定性及其長期可靠性的關鍵因素。這些均是影響產品安全性和耐用性的重要因素。

降低裝置崩潰電壓和互連尺寸會增加低於 16 奈米之製程的 ESD 風險。PathFinder-SC 提供晶片上 ESD 事件的完整的分析,這是所有晶片設計的要求。

PathFinder-SC 的全晶片容量和簡化的單次使用模型可以在一次分析中同時處理數百個域。這比傳統方法快得多,加快獲得結果的時間,並降低由於分區而導致錯誤的可能性。

透過 PathFinder-SC 的佈局型分析和根本原因偵測技術,所偵測到的問題均可快速除錯,再度節省時間並加快上市時間。

PathFinder-SC 包括單個產品中的所有功能,從執行 RC 擷取和 ESD 模擬,到分析根本原因和提供最佳化回饋。它包括內建的 RC 擷取器,無需額外的使用許可或外部工具。

PathFinder-SC 由多個客戶進行矽相關,並透過多個晶圓代工廠的驗證,確保精準度並降低矽風險。

Ansys PathFinder-SC 協助您規劃、驗證和簽核 IP 和全晶片 SoC 設計,以確保抗 ESD 的完整性和穩定性。它識別可能導致元件充電放電模式 (CDM)、人體靜電放電模式 (HDM) 或其他 ESD 事件發生晶片或 IP 故障的設計問題。PathFinder-SC 獲得主要晶圓代工廠認證,確保互連寄生、HBM/CDM ESD 模擬以及電阻和電流密度檢查均準確,以利進行 ESD 簽核。它的佈局型 GUI 有助於快速偵測根本原因和輕鬆除錯。

PathFinder-SC 採用雲端原生基礎架構來架設,可進行彈性運算,並能夠處理超過 1 億個電晶體的全晶片分析。

同時針對數百個電源模式提供全晶片和完整的單次 ESD 分析與除錯。

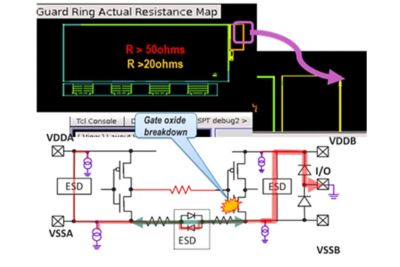

Ansys PathFinder-SC 透過電源/地面網路傳播轉切電流來確認佈局瓶頸,藉此模擬人體充電放電模式 (HBM) 和元件充電放電模式 (CDM) ESD 事件。它為注入任何接墊和互連路徑中的電流建模,以確認無法處理高 ESD 電流的接腳-夾鉗-接腳路徑。

Ansys PathFinder-SC 使用 SPICE 模型和 TLP 曲線以皮秒的解析度進行暫態模擬,提供與矽相關的精準度,有助於將設計風險降至最低。具有驟回的夾鉗在 SPICE 中通常會出現收斂問題;但是 PathFinder-SC 的模擬引擎經過自訂,可以處理驟回,並準確地建立 ESD 裝置觸發模型。已有多個晶圓代工廠和客戶將 PathFinder 的結果與矽相關聯。

Ansys PathFinder-SC 找出可能導致 ESD 故障的佈局問題和連接不平衡狀況。例如未連接至 ESD 夾鉗的凸塊或夾鉗未連接至電源/接地。藉由橫動晶片上任意兩個相關點之間的每條傳導路徑,PathFinder-SC 驗證連接的穩定性,並根據晶圓代工廠或使用者指定的限制檢查電氣特性。成功失敗報告可以交叉探測到佈局。

Ansys PathFinder-SC 的整合式資料建模、擷取和模擬引擎提供簡化的單次 ESD 使用模型 — 在單一工具環境中設置 ESD 規則、執行擷取和 ESD 模擬、分析根本原因並提供修復和最佳化回饋。它使用業界標準資料格式 (GDS、DEF),並在指定要檢查的規則和參數方面提供相當大的彈性。

Ansys PathFinder-SC 在 IP 和擁有超過 1 億個實例的大型 SOC 上檢查 ESD 完整性。它處理數百個電源/接地/訊號網路走線,並在單個模擬中執行電阻和電流密度檢查。根據大小而定,全晶片 ESD 模擬可以在幾小時到一天內完成。PathFinder-SC 建立在彈性運算和雲端原生的基礎架構上,可處理超大型設計。

要避免可靠性問題,務必在標準單元層級、IP 層級和全晶片層級確認高電流熱點。PathFinder-SC 內建的建模功能是以 晶片 ESD 精簡模型 (CECM) 為基礎,它可以在任何層級,從標準單元到全晶片,進行詳細的 ESD 分析。CECM 包括 PG 模型、夾鉗裝置和一個選用的電流簽章。這種精準建模符合任何設計的最高可靠性需求。

Ansys PathFinder-SC 建立在 SeaScape 巨量資料分析平台上,這是專為執行具有 1,000 個 CPU 核心的雲端所設計,具備近線性的可擴充性和極高容量,且每個核心占用的記憶體偏低。

對 Ansys 而言,所有使用者皆能運用本公司產品非常重要,身心障礙者也不例外。因此,我們致力於遵循美國無障礙委員會 (第 508 節)、無障礙網頁內容規範 (WCAG)、自願性產品輔助工具範本 (VPAT) 當前格式等各項無障礙需求。

如果您面臨工程挑戰,我們的團隊將隨時為您提供協助。憑藉豐富的經驗和對創新的承諾,我們邀請您與我們聯絡。讓我們共同合作,將您的工程障礙轉化為成長和成功的機會。立即與我們聯絡,開始對話。