隨著世界對更快、更小、更智慧裝置的需求不斷增加,人們不禁好奇工程師是如何跟上這些變化的。從 4G到5G,再到如今即將到來的 6G,再加上更智慧的手機、電視與手錶,這些都依賴高速網路運作,更別提人工智慧 (AI) 以及因高速數位科技而來的各種期待。這些技術進步的複雜性,清楚展現在我們常用裝置內部元件所需的大量設計投入上。

設計團隊越來越需要新的先進工具,來幫助降低成本並解決可能導致延誤或次級產品的問題。在製造前能精準模擬設計的各個面向,已被證明是快速發展的半導體領域中顛覆性的關鍵。

透過多物理模擬聚焦寄生效應

所有電子裝置內都至少都有一顆由半導體材料矽製成的積體電路 (IC),俗稱為晶片,而多數情況下,裝置內往往會包含好幾顆這樣的晶片。晶片內部是由稱為電晶體的小型電子元件構成於矽基板內,並透過堆疊於矽表面的互連進行連接。製造 IC 可能需要三到四個月,而且一旦出錯就無法修正或修改。因此,如果晶片從代工廠回來後卻無法正常運作,將會造成大量時間與金錢損失。所以,設計必須在製造前經過全面測試。Ansys 多物理模擬提供了完整的 IC 設計解決方案,擁有無與倫比的物理建模能力範圍。這些模擬使其能夠建模多個物理領域間複雜且同時發生的交互作用,而這些作用會顯著影響 IC 的效能。

寄生效應與高速需求

IC 設計中究竟有多少潛在問題?不幸的是,隨著設計速度的提升,出錯的機率也隨之增加。這是工程師在設計能處理當今高頻通訊技術晶片時必須付出的代價。高速設計對不必要、非預期的效應 (稱為寄生效應) 非常敏感,而這些效應往往難以診斷。問題往往在為時已晚時才浮現,並影響積體電路的結構、物理、熱或電磁特性。隨著設計規模不斷增大,加上光子學、三維積體電路 (3D-IC) 等先進功能帶來的新型且複雜的物理交互作用,這些都讓診斷變得更加困難。

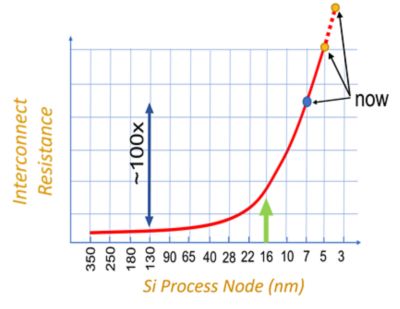

在先進的矽製程中,寄生電阻會顯著增加。

再加上緊湊的時程,工程師所承受的壓力比以往更大。Ansys 模擬能快速分析根本原因,大幅降低時間與成本,使 IC 的開發與測試變得更可控。

使用 Ansys ParagonX 軟體辨識佈局寄生效應

寄生效應有多常見?又該如何定位?寄生效應存在於所有半導體設計中,通常包含兩個基本概念:電阻與電容 (RC)。它們在電路設計中出現,是因為佈局物理與材料特性的必然結果。寄生效應可能導致訊號延遲、功率損耗以及訊號傳真度下降。

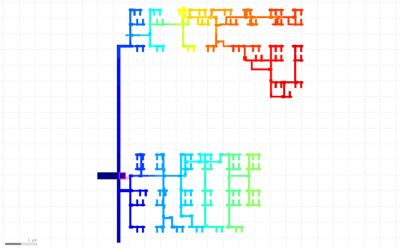

在設計中避免寄生效應的困難點在於很難精準找出問題的真正原因與位置。Ansys ParagonX 積體電路設計分析與除錯工具,透過圖形化回饋與進階分析,幫助定位設計中選定訊號的互連寄生效應,免除模擬整體設計的不確定性。

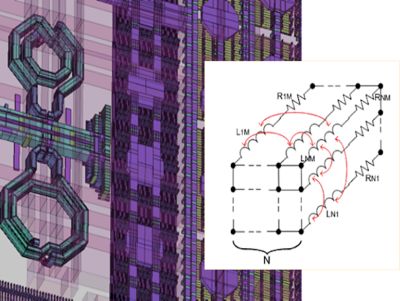

使用 Ansys ParagonX 積體電路設計分析與除錯工具,針對佈局寄生效應進行晶片互連導線的寄生延遲除錯

高速下寄生效應增加

這種精確的模擬方法若能在設計流程早期就用來除錯 RC 寄生效應,便能幫助工程師節省時間,並最終協助找出設計問題的根本原因。

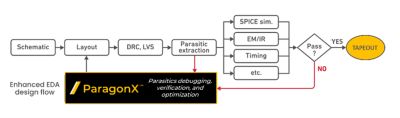

ParagonX 軟體透過強大的分析功能與視覺化回饋,增強了既有的電子設計自動化 (EDA) 工作流程,幫助找出佈局寄生效應對效能、延遲、穩健性與可靠性的影響根源。使用者能更有效率地分析整顆晶片的高階視圖,這對於管理大型設計的頂層互連特別有幫助。這些功能能以視覺化方式精準定位瓶頸與弱點,最終讓設計人員能達到規格目標,並避免設計流程中的延誤。

ParagonX 工具如何整合至既有晶片設計流程的概覽

使用 RaptorX 軟體診斷電磁寄生效應

高速晶片運作於數千兆赫或更高頻率時,對於電感 (L) 寄生效應的考量需求也隨之增加。互感與自感成為工程師的另一大難題,而高頻高速下產生的耦合與串擾等電磁效應更是棘手。隨著裝置與內部元件不斷縮小,寄生效應的影響只會持續放大。例如,訊號在匯流排或訊號線上傳遞時,會因寄生效應而產生失真、延遲,並降低元件之間的整體通訊品質。

電感是一種非局部效應,因為它會同時影響元件及其周邊元素而難以診斷,且其效應會隨著頻率與電磁場的增加而更加顯著。因此,這些現象必須以更的高精度建模。

隨著裝置與內部元件越做越小,可容許的誤差的空間幾乎不存在——真的是字面上的意思。將元件間距拉大以避免串擾與耦合是一種理想解決方案,但在空間有限時,這樣做既昂貴又難以實現。為這些對電磁敏感的元件加上屏蔽是另一種選項,但同樣成本高昂。那麼,工程師要如何在 IC 設計定稿並製造之前,精準找出潛在問題呢?

Ansys RaptorX 矽最佳化電磁求解器,可用於設計分析與建模,讓使用者能在設計階段就納入這些電磁寄生效應。若在設計流程早期使用,這款求解器能幫助使用者及早發現問題,避免在後期才修正而導致嚴重延誤。這款求解器能找出那些直覺上不易察覺、且過於複雜以致無法手算的電磁問題,為 IC 設計流程帶來關鍵的精準度。

使用 Ansys RaptorX 矽最佳化電磁求解器,進行高速射頻電路的電阻 (R)、電感 (L)、電容 (C) 建模與設計分析

RaptorX 求解器是專為晶片內 IC 應用所設計的。它的高精度分析,讓更小型、更高空間效率的設計成為可能,例如能將電路放置於大型電感線圈之下。傳統上,這些電路會被保持分離,以避免交互作用。但透過 RaptorX,這些交互作用能被精準模擬與預測,讓「電路置於電感下方 (CUI)」的設計方法能夠實現大幅的成本與空間節省。

先進的鰭式場效電晶體 (finFET) 製程技術,因佈局依賴效應 (LDE) 而增加了複雜性,而這些效應必須納入分析才能保證準確度。LDE 指的是有源元件的行為或特性,會受到鄰近元件放置方式的影響。因此,元件擺放位置會影響電晶體的行為。這個複雜因素讓先進製程節點的設計更難以準確分析。

藉由晶圓廠認證的準確度,RaptorX 模擬能將設計時間大幅縮短,將模擬週期從數天甚至數週減少到僅需數小時。

以先進模擬應對設計挑戰

面對關鍵裝置,特別是其內部元件不斷演進的技術環境,工程師正與時間賽跑以跟上腳步。具備模擬設計與更早找出根本原因的能力,讓設計人員能進行更快速、更精準的除錯。使用者可以依靠 Ansys ParagonX 與 RaptorX 求解器,提升設計品質並縮短設計週期。

進一步瞭解如何善用 Ansys 產品,最佳化您的類比與混合訊號裝置設計。