簡要規格

Ansys Lumerical INTERCONNECT 可與 Ansys Lumerical CML Compiler、Ansys 多物理求解器,以及第三方 EDA 和布局工具廠商順暢連動,實現快速、準確、可擴充的光子 IC 設計。

Ansys Lumerical INTERCONNECT 能模擬古典與量子光子積體電路,同時允許在多個 EDA 平台上採用光子與電子電路的共同設計和共同模擬。

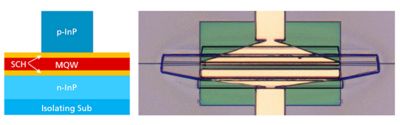

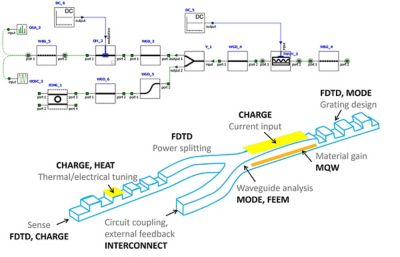

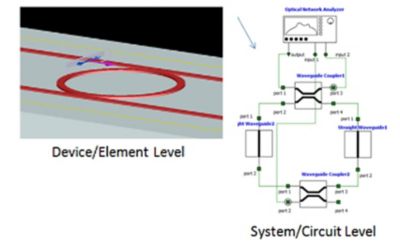

INTERCONNECT 為經典與量子光子積體電路 (PIC) 提供完整全面的設計環境。它具有業界頂尖的電子光子共同設計、共同模擬功能,以及 SDL,LVS 和 DRC 等基本設計工作流程,並與多個 EDA 平台相容。設計師可以利用 Lumerical 的 PDK 驅動平台,有效率地建立可大量生產與可自訂的光子設計,同時考慮相關的電子、封裝和連結。

加入 Ansys Optics 對話

Ansys Lumerical INTERCONNECT 可與 Ansys Lumerical CML Compiler、Ansys 多物理求解器,以及第三方 EDA 和布局工具廠商順暢連動,實現快速、準確、可擴充的光子 IC 設計。

2026 年 3 月

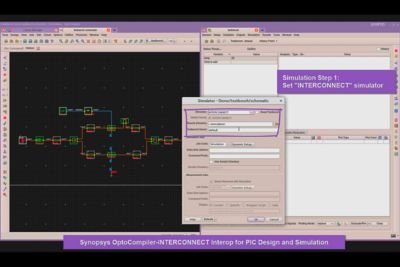

Ansys Lumerical INTERCONNECT 2026 R1 版本導入順暢的 PyLumerical 自動化、Synopsys OptoCompiler 互通性,以及在降低記憶體使用量同時提供更快速的模擬,為複雜的光子 IC 設計與進階應用帶來可靠的模擬結果。

Synopsys OptoCompiler 使用者現在可在 Synopsys PrimeWave 中選擇 Lumerical INTERCONNECT 求解器作為光子電路模擬器。 光子 IC 設計人員可在 OptoCompiler 中繪製電路圖,並根據 INTERCONNECT Compact Model Library 執行 INTERCONNECT 時域模擬。

透過以 Python 為基礎的解決方案 PyLumerical,順暢地自動化 Lumerical 工具。與 PyAnsys 生態系完全相容,可整合 FDTD、MODE、Multiphysics、INTERCONNECT,以及 OptiSLang 和 Speos 等其他 Ansys 工具,另外也可搭配開源 Python 程式庫。透過這種高效率的現代方法,簡化工作流程並強化多物理模擬。

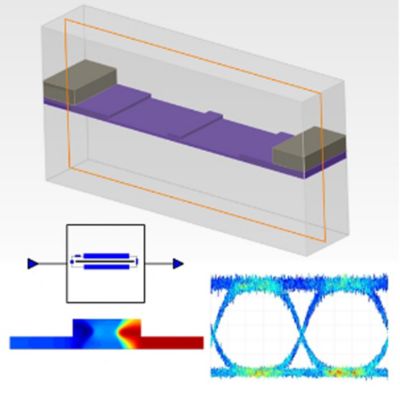

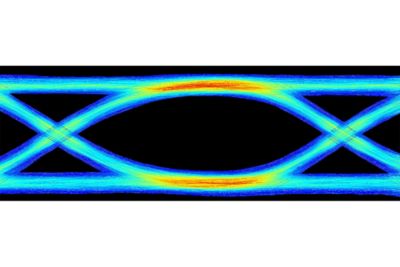

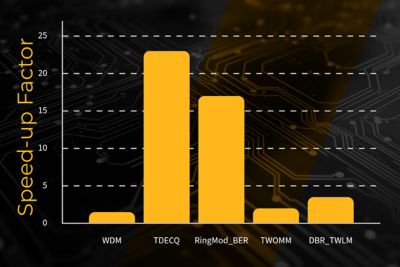

即使面對複雜且高需求的電路,也能以更快的速度與更低的記憶體使用量,提升模擬效能。非常適合 WDM 架構、TDECQ 分析與 Ring Modulator BER 等進階設計,並可高效率處理互連的元件。運用專門的最佳化工具,針對需要精準度與一致性的大規模或長時間應用,獲得可靠結果。

Ansys Lumerical INTERCONNECT 為經典與量子光子積體電路 (PIC) 提供完整全面的設計環境。

體驗業界最先進、最具延伸性的平台,可共同設計電子積體電路和 PIC,並進行共同模擬。

採用 INTERCONNECT 龐大的模型資料庫、立即可用的晶圓廠已調校模型或自訂的精簡模型,來設計並最佳化多種積體光路。

對 Ansys 而言,確保所有使用者皆能運用本公司產品非常重要,身心障礙者也不例外。因此,我們致力於遵循美國無障礙委員會 (第 508 條)、Web內容無障礙指南 (WCAG)、與目前自願產品無障礙工具範本 (VPAT) 的格式等各項無障礙要求。

如果您面臨工程挑戰,我們的團隊將隨時為您提供協助。憑藉豐富的經驗和對創新的承諾,我們邀請您與我們聯絡。讓我們共同合作,將您的工程障礙轉化為成長和成功的機會。立即與我們聯絡,開始對話。