快速规格

Ansys Totem和Totem-SC是晶体管级电源噪声和可靠性分析平台,适用于模拟混合信号IP和完全定制设计。他们通过RedHawk-SC为SOC级别的电源完整性签发创建IP模型,并为芯片级和系统级的电源传输网络生成紧凑型芯片模型。

Ansys Totem可为基于云原生弹性计算基础设施构建的模拟和混合信号设计提供电源噪声和可靠性签发领域,是久经考验和值得信赖的行业领导者。

Ansys Totem是业界值得信赖的黄金标准压降和电迁移多物理发解决方案,适用于晶体管级和混合信号设计。它已通过所有主要代工厂的认证,可用于低至3纳米的FinFET节点,并有数千次流片的记录。Totem-SC是基于SeaScape的Totem的云端原生版本,可为其提供超高速度和处理最大的全芯片分析的能力。

Ansys Totem和Totem-SC是晶体管级电源噪声和可靠性分析平台,适用于模拟混合信号IP和完全定制设计。他们通过RedHawk-SC为SOC级别的电源完整性签发创建IP模型,并为芯片级和系统级的电源传输网络生成紧凑型芯片模型。

NXP工程师为数字汽车无线电设计了一个成本更低,音质更好的芯片。

签发分析通过避免硅片中代价高昂的错误来降低项目风险。精确的多物理仿真通过消除浪费性的余量和更好的硅相关性来提高设计性能。

Totem值得信赖的多物理签发分析,降低项目和技术风险的有效方法。其算法经过所有主要代工厂的认证,适用于所有低至3纳米的FinFET工艺,并在数千此流片中得到了验证。

Totem-SC基于云端原生SeaScape™体系结构,可对超大型设计进行全芯片功耗分析。Totem-SC列出了数千个具有适度内存要求的CPU内核,可提供与Totem相同的快速结果。

Totem的高级可靠性分析(如热敏EM和统计EM预算)提高了汽车设计的安全性。Totem还在从早期IC原型设计阶段到系统级的所有阶段提供价值。早期分析可实现比签发时更便宜,更有效的优化。代工厂认证的硅相关仿真结果使设计人员能够通过避免浪费和昂贵的过度设计来获得更高的性能和更低的功耗。

Ansys Totem是晶体管级功率噪声和可靠性分析平台,用于对模拟混合信号IP和全定制设计进行全面的功率完整性分析。Totem可以使用RedHawk-SC为SoC级签发创建IP模型。Totem分析从早期的原型到签发,可以处理各种设计样式,如SerDes,数据转换器,电源管理IC,嵌入式存储器,DRAM, 闪存,FPGA和图像传感器。它分析基底噪音,RDSON,自热和ESD (使用Ansys Pathfinder™)。Totem-SC的云端原生弹性计算体系结构能够以适中的内存消耗处理非常大的设计。

Ansys Totem和Totem-SC为模拟混合信号签发设置了标准

•早期原型设计

•数百万的xtor flat

•使用Totem-SC进行云处理

•增量分析和假设分析

•同时仿真数字和模拟

•矢量或无矢量活动

•内置PG网络提取

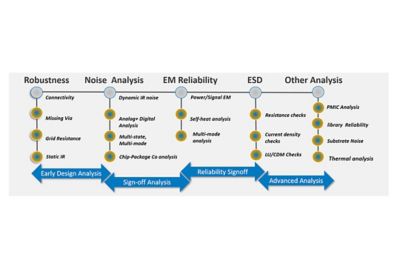

Ansys Totem/Totem-SC提供的功能包括电力网薄弱分析,缺少的vias,P2P检查以及各种早期静态和动态IR和EM分析,这些功能可以在设计早期阶段在LVS清理之前突出设计弱点。这使设计人员可以决定电网规划,bump 摆放,去耦电容优化,关键信号上的EM等

Ansys Totem/Totem-SC可准确地签发大型混合信号设计。诸如本地处理位置和路由数字数据库,以及复杂AMS的分层分析等关键功能,通过自下而上的每个块验证以及用于顶层分析的综合多状态晶体管级或抽象宏模型简化了整体流程。矢量模拟或无矢量模拟可以调整功能状态以模拟最坏情况下的应力场景。

Ansys Totem/Totem-SC提供了全面的EM签发,其中包括功率/信号EM分析,焦耳热建模,线耦合和FinFET的自热及其对互连的影响。所有主要代工厂均已启用该流程,所有从事FinFET设计的客户均已使用该流程。Totem中还启用了统计EM预算,以满足汽车和其他关键任务应用的需求。

IP集成是SoC设计人员面临的最大挑战之一。在两种不同模式下运行的同一IP会有非常不同的压降。Totem和Totem-SC在顶级压降分析中为不同操作模式的IP精确建模和表征。IP模型包括电气和物理属性,以及RedHawk-SC在SoC级别上对电源完整性签发的任何嵌入式限制。

Ansys Totem/Totem-SC的GUI提供了高级查询和调试功能,包括可自定义的地图和调试视图,以帮助识别和修复设计缺陷。它们还支持模拟分析,以便在最终确定设计更改之前快速修复设计。与传统流程相比,这显著加快了周转速度,传统流程中的修复首先需要通过昂贵的LVS和RC提取,然后才能进行EM/IR分析。

Ansys Totem-SC基于SeaScape大数据分析平台构建,该平台的设计主要用于在数千个CPU内核上执行云计算,具有近似线性的可扩展性。这为Totem-SC提供了极高的容量和快速的执行速度,每个内核的内存较低,并且可以即时启动。

让所有用户(包括残障人士)都可以访问我们的产品对Ansys至关重要。因此,我们努力遵循基于美国访问委员会(第508节),Web内容可访问性指南(WCAG)和自愿产品可访问性模板(VPAT)的当前格式的可访问性要求。

如果您面临工程方面的挑战,我们的团队将随时为您提供帮助。我们拥有丰富的经验并秉持创新承诺,期待与您联系。让我们携手合作,将您的工程挑战转化为价值增长和成功的机遇。欢迎立即联系我们进行交流。