L’affidabile analisi multifisica per le verifiche sign-off di Totem è un modo efficace per ridurre i rischi legati a progetti e tecnologie. I suoi algoritmi sono certificati nell'accuratezza da tutte le principali fonderie per tutti i processi finFET fino a 3nm e sono collaudati in migliaia di tapeout.

Totem-SC è basato sull'architettura SeaScape™ nativa per il cloud, per l'analisi completa di power integrity di progetti di dimensioni molto grandi. Totem-SC può utilizzare migliaia di core CPU con requisiti di memoria modesti per offrire risultati rapidi con la stessa accuratezza di Totem.

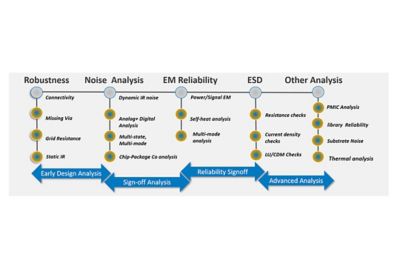

Le analisi avanzate di affidabilità di Totem, come il Thermal-aware EM e il budget statistico EM, migliorano la sicurezza dei progetti automotive. Totem fornisce inoltre valore in tutte le fasi, dalle prime fasi di prototipazione di un IC fino a livello di sistema. L'analisi nelle fasi preliminari del progetto consente ottimizzazioni più semplici da realizzare e di maggiore impatto rispetto a quelle possibili al momento delle verifiche di sign-off. I risultati di simulazione correlati al silicio e certificati dalle fonderie offrono ai progettisti la sicurezza necessaria per ottenere prestazioni più elevate e ridurre il consumo energetico evitando sprechi e costosi over-design.