想象一下,如果您是一位经验丰富的半导体工程师或设计人员,为新的集成电路(IC)生成了对称网络布局,但在布局后的SPICE仿真中发现了误判的电气不匹配问题。由于该结果显示并不清晰直观,您只能返回到设计中检查是否存在非对称性,但仍然毫无头绪。那么,到底是怎么回事呢?

原来,这种误判的电气不匹配效应是由寄生电阻器网络节点上寄生耦合电容器的分布差异引起的,而这种分布差异是由寄生提取和寄生提取工具引入的伪影所导致的。

我们将在本文中为您提供一些实用建议,以帮助识别这些误判的不匹配情况,并将它们与布局差异所导致的真正的不匹配情况区分开来。Ansys ParagonX寄生提取软件可帮助您避免这些伪影,并确保布局后仿真和IC设计流程的可靠性。

IC设计中的器件和网络匹配

许多模拟和射频(RF)集成电路都依赖于器件和网络相匹配这一概念。1,2此类电路的示例包括StrongARM锁存器、传感放大器、差分对、电流镜、多相时钟等。匹配的网络和器件可以提供一定的设计裕量,确保电路能够应对不可避免的工艺变化。

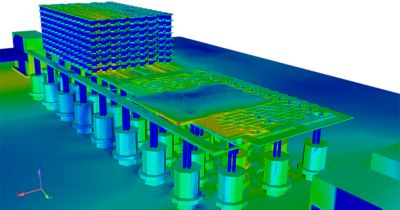

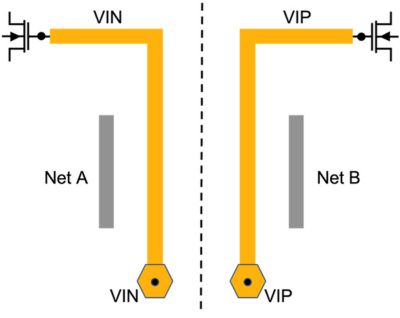

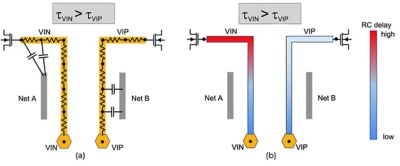

为了实现完美的网络匹配,设计人员会通过绕X轴或Y轴翻转设计以及移动或旋转单元的方式来创建对称布局,如图1所示。

然而,由于设计规则、导线可布线性和几何结构的约束,几乎很难实现完美的对称和匹配。这也是为什么在标准的布局后设计流程中,工程师通常会执行寄生提取来验证器件和网络的匹配情况,然后再进行布局后电路仿真。如果仿真显示了良好的预期结果,则您已经获得了最佳的对称性和匹配性。如果测量的信号中存在一些偏移、不匹配或差异,则匹配性不够好,则需要改进布局。

真正的问题

实际的挑战在于:即使网络是完全对称和匹配的,布局后的仿真仍然经常会显示出电气行为的差异。一个典型的情况是,两个网络的电容和电阻数值匹配良好,但在RC延迟(用希腊小写字母τ表示)方面却存在显著的不匹配。根据常识和基本的物理知识,如果电容和电阻相匹配,则延迟也应当匹配。所以,在这种情况下,延迟不匹配就违反常理了。

图1:匹配网络VIN和VIP的布局。输入端口为VIN和VIP,目标点为MOSFET的栅极。这些网络及其环境是对称创建的,以确保寄生电阻、耦合电容和RC延迟匹配。

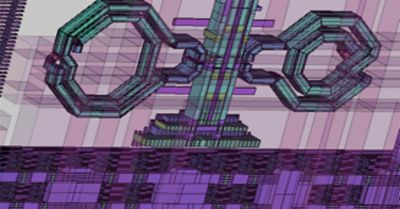

图2:(a)寄生单元(电阻和电容)的可视化。注意不对称性,即网络VIN和VIP耦合电容分布之间的差异。(b)网络布局上的RC延迟的可视化。由于耦合电容集中在网络VIN的远端(形成端口VIN)和网络VIP的近端,因此VIN上的延迟大于VIP上的延迟。

事实证明,问题在于寄生提取软件。具体而言,延迟不匹配的根本原因与寄生提取工具如何在电阻网络的节点上分配耦合电容有关。由于某种原因,耦合电容的分布非常不对称,如图2所示。

最有可能导致这种不对称性的原因是,提取工具使用的计算几何算法具有各向异性。这些算法,比如扫掠(或扫描)线或多边形边界遍历,都具有首选方向,例如从左到右、从上到下或从顺时针到逆时针。因此,这些算法将布局视为平面系统,而不是3D系统,这就导致系统失去了原本的层级结构和单元转换特性,而这些特性在理论上可以用于变换偏好方向。

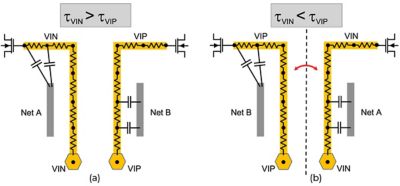

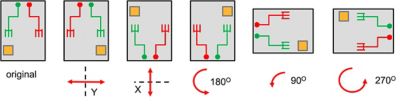

为了研究这一假设,我们进行了一系列的实验,包括分析布局后网表并对多个GDS文件进行布局后仿真。我们将原始的DSPF文件用作参考,并把它与通过各种变换后(即相对于X轴和Y轴的对称反射,以及旋转90度、180度和270度)获得的DSPF文件进行比较。对称变换的结果如图3所示。

图3:(a)原始的和(b)翻转后的GDS文件的RC寄生效应。案例(a)和案例(b)中的网络VIN和VIP的耦合电容分布完全相反。案例(a)中左边网络和案例(b)中右边网络的耦合电容分布相同。

正如预期的那样,原始布局和翻转后布局的左边网络的耦合电容分布相同,右边网络的分布也是相同的。然而,由于网络VIN和VIP从原始布局变为翻转的布局后互换了位置,因此案例(a)的网络VIN上的耦合电容分布现在变成了案例(b)中网络VIP的耦合电容分布,反之亦然。

这种电容分布的变化与VIN和VIP上的RC延迟仿真结果密切相关。案例(a)中网络VIN的RC延迟(τ)大于网络VIP的RC延迟,但案例(b)中网络VIN的RC延迟(τ)小于网络VIP的RC延迟。同样地,我们发现布局后的电路仿真也存在差异,即案例(a)中网络VIN的转换时间明显比网络VIP的转换时间要长,而案例(b)中网络VIN的转换时间明显比网络VIP的转换时间要短。如上所述,这表明了对称网络VIN和VIP之间的电气不匹配是寄生提取工具引入的伪影所导致的。

当然,如果对网络VIN和VIP进行布局变换后,其耦合差异和RC延迟差异并没有改变其符号,则这种差异是由真实的布局不匹配引起的,需要在布局层面进行修复。

在寄生电阻器网络上实现耦合电容器分布

这个实验,可能是首次有研究团队尝试对寄生提取的伪影与对称布局的各向异性、非对称耦合电容分布的相关性进行研究。

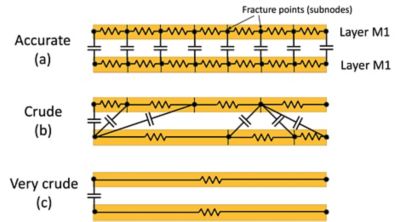

团队利用三种主要的寄生提取工具,在面向不同设计、技术、代工厂的仿真中观察到了误判的不匹配效应。这种误判的各向异性的严重程度因提取工具而异,其原因在于三种寄生提取工具的耦合电容器分布质量不同,分别是准确、粗略和非常粗略,如图4所示。

每种寄生提取工具都会试图最大限度地缩小寄生RC网络的尺寸,以加速布局后的仿真(适用于SPICE、EMIR、时序和其他工具)。此外,网表尺寸(仿真时间)和精度之间始终存在权衡。不同的寄生提取工具在“物理建模精细度”和“提取精度”方面各不相同。

图4:寄生电阻器网络节点上的耦合电容分布。案例(a)是最准确的,案例(b)不太准确,案例(c)非常粗略。

仿真和分析结果

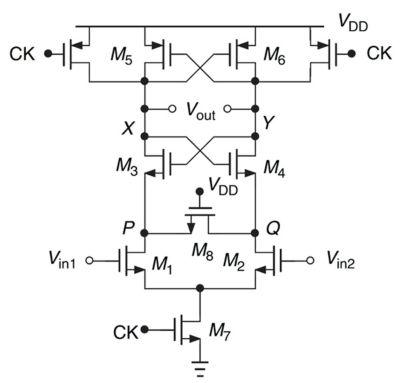

对于采用5nm FinFET技术的StrongARM锁存器3(参见图5)的布局后SPICE仿真显示,器件M1和M2的转换时间存在约500 fs的差异,该值远高于设计规格要求的上限(30 fs左右)。该布局相对较小,通过视觉检查并未发现任何不对称性。设计人员和布局工程师对布局进行了多次迭代,试图消除仿真中的不匹配。然而,经过了两个多星期,他们仍然毫无所获。

将布局绕Y轴翻转后,生成的后布局网表中出现了符号相反的不匹配现象:转换时间差异为-370 fs。该结果就是一个清晰明了、令人信服的论据,即+500/-370 fs的不匹配是由寄生提取工具的伪影造成的。

使用ParagonX电子设计自动化(EDA)工具对网络不匹配进行分析后,确认了网络in1和in2之间的RC延迟差异超过15%。该差异导致原始布局和翻转布局的符号发生了变化。然后,工程师使用ParagonX软件对耦合电容进行可视化,进一步证实了其分布存在明显的不对称性。(出于第三方保密原因,本文中无法显示这些图表。)

有趣的是,网络in1和in2的电阻以及网络对网络耦合电容都是匹配的,误差非常小。电阻的差异小于0.05%,耦合电容的差异小于0.2%。这是我们在许多布局后网表中观察到的常见效应,虽然匹配网络上的电容和电阻非常接近,但由于本文中讨论的效应,RC延迟可能截然不同。

我们认为,0.2%的电容差异是由基于规则(基于模式匹配)的电容提取不够精确所导致的。如果使用基于随机游走的场求解器(FS),并设置由用户控制的精度目标,可以获得更高的电容提取精度。因此,对于电容匹配(或用于SAR ADC中电容器阵列的二进制或非二进制加权)对电路运行至关重要的网络而言,始终建议使用选定的网络FS提取模式。

探讨结果

图5:StrongARM锁存器的原理图。网络in1和in2中的RC延迟应该相匹配。

布局后电路仿真被认为是分析和模拟定制晶体管级IC设计的黄金标准。我们观察到误判不匹配效应后,会有一个有趣的问题:布局后仿真的准确性如何?显然,布局后仿真的精度取决于寄生提取工具的精度。电容和电阻提取通常相当准确,但如果在寄生电阻器网络节点上的耦合电容分布过于粗略,可能导致瞬态和交流(AC)仿真中的误差达到~500 fs(或更多)。这一发现具有重要意义,表明了SPICE仿真十分可靠准确,能够用于精确和高速的模拟设计、时序分析和其他应用。因此,行业至少需要确定一种方法来检测、调试、分析或解决上述问题。

同样重要的是,由提取伪影导致的误判不匹配,可能会掩盖真正的布局和电气不匹配,而后者是由匹配网络的布局和环境的差异造成的。如果存在误判的不匹配,那么就很难甚至无法检测真正的不匹配。另外还有一个高风险因素,那就是如果误判不匹配和真正的不匹配刚好相互抵消,那么仿真结果可能会显示为匹配良好,或者看起来问题很小。

实用建议

请考虑以下建议:

- 对于电路设计人员和布局工程师:

a.通常要更多地关注不匹配,尤其是由不正确的寄生提取造成的误判不匹配。

b.提高对这些效应的认知。这要求EDA工具供应商提高准确性,并消除寄生提取中与耦合电容器分布相关的伪影。

c.使用场求解器,准确、可控地提取匹配网络的电容(如果电容匹配至关重要)。

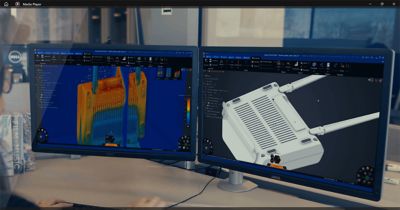

d.使用ParagonX软件或其他EDA工具,主动检查和验证布局后网表中的网络和器件匹配,调试此类问题,并改进布局匹配。

- 对于EDA工具供应商:提高寄生提取工具的准确性,特别是提升耦合电容器分布的质量。

- 对于代工厂:对与网络匹配和耦合电容器分布质量相关的寄生提取工具,进行更加全面的验证和认证。

- 对于EDA研究人员:提供更好的算法和方法,在不显著增加后布局网表规模的前提下,提高其精度。

- 对于所有人员:检查设计流程中是否存在可能由寄生提取造成的误判不匹配:

a.通过对原始布局实施对称变换来创建布局(参见图6),例如:

i.绕X轴翻转。

ii.绕Y轴翻转。

iii.旋转180度、90度或270度(如果DRC允许)。

b.执行寄生提取。

c.使用ParagonX软件比较原始布局和转换布局的布局后网表。

i.与SPICE仿真相比,ParagonX软件可以更快速、轻松地检测和调试不匹配。

d.如果无法获得ParagonX软件,请使用布局后的SPICE仿真或其他分析工具(STA等)来比较两个布局后网表。

e.如果存在显著的差异表明是误判不匹配:

i.对布局进行视觉检查(如果可能)。

ii.将发现结果报告给寄生提取工具供应商和代工厂。

图6:有助于识别误判网络不匹配的布局转换。电气特性在这些变换下应保持不变,因此寄生电容、电阻、延迟、器件和SPICE仿真也应该是不变的。

进一步了解Ansys ParagonX IC布局寄生分析和调试软件如何帮助您解决IC设计中误判的电气不匹配问题。

参考资料

[1] “The art of analog layout,” 2nd ed., A. Hastings, Prentice Hall, 2005.

[2] “CMOS IC Layout: Concepts, Methodologies, and Tools,” D.Clein, Newnes, 1999.

[3] “The StrongARM Latch” (A Circuit for all seasons), B.Razavi, IEEE Solid-State Circuits Magazine, v. 7, no.2, p. 12-17, 2015.

Advantage博客

Ansys Advantage博客(The Advantage Blog)由Ansys专家和其他技术专家撰写,让您随时了解Ansys如何为创新赋能,推动人类踏上伟大征程。