Ansys博客

May 16, 2023

低功耗IC设计:技术方法与最佳实践

低功耗集成电路(IC)设计是现代电子产品的一个重要方面,因为它可以延长电池使用寿命并降低设备的能耗。随着电池供电设备市场的不断增长,芯片设计人员有必要认真考虑采用不同的方法来降低IC的功耗。有几种方法可用于降低IC的静态和动态功耗。直流电流和泄漏电流是静态功耗的来源,而动态功耗与频率有关,它来自晶体管开关和短路功耗。

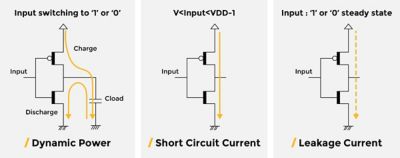

图1:互补金属氧化物半导体(CMOS)电路中的功率组件

为了创建低功耗设计,设计人员必须减少产生整体功耗的每个单独功率组件。图1同时显示了动态和静态功耗特性。互补金属氧化物半导体(CMOS)逆变器的动态充电使功耗与时钟频率成正比。晶体管在无活动时的功率泄漏会构成静态功耗。

低功耗设计人员可以通过控制供电电压、降低电路复杂性和时钟频率、监控直流电流源和开关节点的电容来降低总功耗。所有因素都相互关联,因此设计人员必须通过测试和使用低功耗设计方法来优化设计性能,从而在这些因素之间进行权衡。

低功耗设计的技术方法与最佳实践

时钟门控

一种降低设备功耗的方法是在寄存器传输(RTL)级调整设计。这是降低动态功耗的最常用方法之一。在RTL级,当晶体管改变其逻辑状态时,或当电源用于负载电容充电时,都会消耗功率。总动态功耗为:

Pdynamic = Pcap + Ptransient = (CL + C) Vdd 2 f N3

其中,CL是负载电容,C是芯片的内部电容,f是工作频率,N是开关位数。在不需要时,通过门控时钟可以轻松减少动态电流。与其使用AND/NOR门,不如使用基于锁存器的时钟门控,以避免任何额外的功耗。关闭IC某些部分的时钟信号可以大幅降低功耗,因为这些区域的晶体管不会开关和消耗功率。

电源门控

IC中的所有模块并非一直同步工作;这取决于它们在设备中的应用。如果某个模块在特定情况下不提供功能,则无需为其供电。通过关闭非功能块的电源,可以降低功耗。为了有效地运用这一方法,设计人员可以使用隔离模块来防止来自电源门控模块的不必要信号。

频率门控

我们知道,芯片由多个模块组成,每个模块并不需要在最高工作频率下运行。最佳方法是根据各模块的频率要求对其进行隔离,并为不同的模块提供不同的时钟信号。这种方法可以大幅降低IC的局部动态功耗。

多电压设计

在设计中,运行各模块所需要的功率都不尽相同。您可以根据模块的性能及其电压要求对芯片进行分区。电压要求越高,功耗就越大。通过创建具有不同电压输入的电压岛,可以轻松降低IC的整体功耗。

动态电压和频率调节

电压岛技术有一个局限性——即一旦设计了模块的供电电压,以后就无法更改了。动态电压调节技术为设计人员提供了灵活性,可在以后根据要求更改电压。设计人员可对稳压器进行编程,使其根据不同的电流改变对不同模块的供电。同样,电压调节可以与频率调节相结合,使设计人员能够在软件程序的帮助下修改为每个模块提供的时钟信号。

功耗降低

到目前为止,最重要的功耗降低技术是降低芯片的供电电压。动态开关电源在FinFET设计中占主导地位,与供电电压的平方成正比,因此极大地推动了超低电压(ULV)工艺的发展。

泄漏功耗权衡

泄漏功耗是前FinFET技术中的一个重要功耗,最好使用多Vt库进行控制。这些库为每个电池提供两个或三个版本,每个版本都具有不同的性能/泄漏权衡。这样设计人员就可以在时序关键路径中使用快速、泄漏的电路单元,而在不太关键的路径中使用较慢、低泄漏的电路单元。

总的来说,有多项技术可用于降低IC的功耗。通过实施这些技术并使用适当的设计和仿真工具,设计人员可以应对这些挑战。Ansys RedHawk-SC等工具使工程师能够在各个设计阶段对设计行为进行仿真和预测,从而设计出更节能、具有更长电池使用寿命的低功耗IC。

低功耗设计挑战

- 压降裕量变得非常小,特别是在超低电压设计下尤为突出。这一发展使得压降(IR)签核验证成为了所有现代IC设计的重要组成部分。

- 低供电电压使路径时序更容易受到动态压降(DVD)的影响。此外,分析DVD时要有足够的覆盖范围,以捕获所有可能的开关场景,这也是一项非常艰巨的任务。谨慎的压降分析至关重要,它有助于最大限度地减少DVD对时序的影响,并避免因意外的IR压降影响而导致频率损耗。

- 多电压区域需要精心管理,以确保不同电压区域之间的正确信号转换和信号完整性。UPF标准旨在帮助应对这一挑战。

- 当再次打开某模块时,电源门控会引入包括电气和逻辑等极具挑战性的转换现象。

- 在尽可能接近时钟配电网络根部的位置实施时,时钟门控最为有效,但这也受限于使能信号时序能否按时到达的可行性。这就需要在实现能效与设计优化工作之间进行权衡。

任何功耗分析的有效性都与电路活动密切相关。然而,为了生成一个现实且具有代表性的活动场景,以捕获实际应用中所有模式下的所有可能的功耗状态,这并非易事。一个常见的错误是使用功能验证活动矢量(acitivity vectors)来计算功耗;这是误导性的,并且与功耗分析无关。良好的活动矢量可以手动生成,也可以由电源工具(“无矢量”)自动生成,或者由运行实际应用的硬件仿真器生成。

RedHawk-SC是一款广泛用于IC设计功耗分析的软件工具。它提供了一套综合全面的功能来准确地预测和分析芯片中的压降,从而帮助解决这一问题。RedHawk-SC使用复杂的算法对芯片供电网络的行为进行建模,同时考虑到片上电阻、电容和电感等因素。这使IC设计人员能够识别潜在的压降热点,并仿真芯片在各种工作条件下的行为。在设计低功耗IC时,设计人员必须考虑供电网络的各个方面,并在设计时预测电压行为。

如需了解更多信息,请访问Ansys RedHawk-SC主页或查看“半导体电源完整性分析与仿真基础”。