超大型類比與混合訊號晶片是先進的積體電路 (IC),能將類比與數位元件無縫整合於單一顆半導體晶片上。這些創新的混合訊號 IC 能促進兩者間的流暢互動,大幅提升晶片的整體效能與功能。

與目前為人工智慧與圖形處理所生產的大型數位晶片相比,大多數類比與混合訊號 (AMS) 半導體設計相對規模較小。數位晶片在單一晶片上輕易就能整合超過十億顆電晶體,而 AMS 晶片通常只包含數千顆。這種差異主要來自於影響類比電路行為的複雜多物理交互作用。

類比效應往往具有高度非線性,且對於實體佈局的細節極度敏感。像電感這樣的重要電性參數,甚至可能受到晶片上遠處電流流動的影響。晶片工程師與模擬工具都難以處理並理解這種複雜性,而這自然限制了類比電路的規模。

類比工程師仰賴電子設計自動化 (EDA) 軟體工具來設計晶片,但這些工具的容量通常也受到限制。這是因為類比模擬引擎 (例如電磁分析) 很難擴展到某一特定層級以上。

SK Hynix 的 HBM3 高頻寬記憶體,採用 12 層 3D 堆疊。圖片來源:SK Hynix

先進製造推動對類比解決方案的需求

近年來 AMS 領域經歷了巨大的演變,出現了需要完整類比分析的超大型半導體裝置。其中的範例包括高頻寬記憶體 (HBM),例如 HBM4;先進製程節點上的現場可程式化邏輯閘陣列 (FPGA);以及互補式金屬氧化物半導體 (CMOS) 影像感測器 (CIS)。此外,整個半導體產業正廣泛採用 2.5D (並排) 與 3D (堆疊) 多晶粒封裝技術。這些龐大半導體系統中的十數顆晶片,是透過稱為「中介層」的大型連接基板相互連接。

AMD 的 Versal 現場可程式化邏輯閘陣列 (FPGA),整合高頻寬記憶體模組 (HBM)。圖片來源:AMD

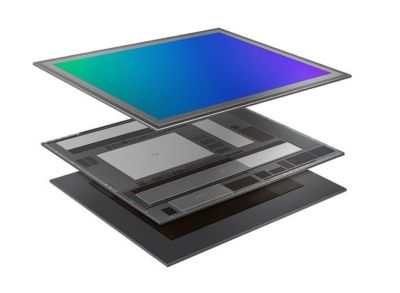

許多設計雖名義上是數位的,但實際上可能需要大量類比模擬才能確保可靠度。它們的規模也相當龐大 — 常用於高效能運算 (HPC) 應用的 HBM4 記憶體模組就包含超過 640 億顆電晶體。應用於小量工業用途的最大 FPGA 含有超過 400 億顆電晶體。應用於數位相機與智慧型手機的 CMOS 影像感測器,是市面上最先進的 3D-IC 多物理堆疊之一,擁有超過 1,000 萬個像素。而在 3D-IC 封裝中連接眾多晶片的中介層,則包含數百萬條訊號線。

Samsung 的 ISOCELL CMOS 影像感測器 (CIS),展示了一顆影像感測晶片堆疊於資料處理晶片之上。圖片來源:Samsung

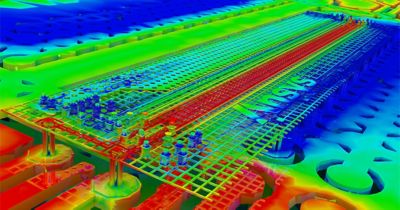

這種演變的原因源自強大的市場趨勢。先進製程節點讓超高頻的數位訊號成為可能,但這也為類比設計帶來全新的挑戰。這些情況無法透過傳統的電阻-電容 (RC) 建模來準確模擬。在這種速度下,完整的電磁建模 (包含電感 (L) 與金屬屏蔽) 變得不可或缺,而這需要類比模擬工具來完成。

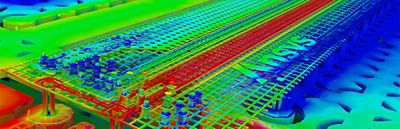

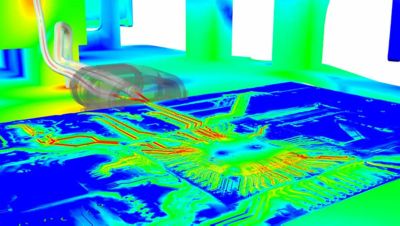

Ansys HFSS 對 3D-IC 多晶粒封裝中介層的電磁模擬結果

另一股推動趨勢是當今裝置中無所不在的影音應用,這讓高解析度影像感測器成為關鍵。這些裝置同樣需要依靠類比分析來支援光學應用、數位成像用的電荷耦合元件 (CCD),以及高速輸入/輸出 (IO)。FPGA 所具備的可程式化邏輯與高速連線功能,也是名義上屬於數位電路,但實際上需要透過類比工具分析的例子。嵌入式記憶體、HBM、CIS 與 FPGA 全都是數百萬電晶體規模的超大型設計,遠遠超過傳統 AMS 晶片的尺寸。

類比設計新時代的新工具

大型電路的設計人員需要新一代的類比工具,能在高速與先進製程節點下可靠地預測類比行為。傳統方法僅針對小區塊進行分析,但這些超大型設計需要完整晶片模擬,才能確保結果的可靠性與準確性。Ansys 與全球頂尖的矽晶供應商緊密合作,開發出能解決這些挑戰的工具與技術。

第一項技術重點是徹底提升基礎模擬演算法的速度與容量。廣受使用的電磁工具,例如 Ansys HFSS 晶片到系統電磁模擬平台與 Ansys RaptorX 矽最佳化電磁求解器,現在具備先進的網格融合技術,能一次快速模擬擁有數百個連接埠的大型模型,而且完全不犧牲準確性。

設計人員面臨的另一個新興類比挑戰,是驗證 3D-IC 中多晶片連接的靜電放電 (ESD) 電路。Ansys 開發了 Ansys PathFinder-SC 靜電放電可靠性簽核平台,專為大型 IP 與 3D-IC 設計,並獲得台積電認證,能用於多晶粒 ESD 簽核。隨著設計規模不斷擴大,電源完整性與壓降分析的運算需求也日益增加。Ansys Totem-SC 電源完整性簽核平台,專為大型類比、混合訊號與 3D-IC 而設計,是應對超大型 AMS 設計的專用解決方案。

其次,Ansys 與主要晶圓廠密切合作,全面支援在 10 奈米及以下先進 FinFET 節點設計時所出現的佈局依賴效應 (LDE)。這對於在先進節點中準確預測電容與電感至關重要,因為 LDE 可能造成 25% 以上的偏差。大型 AMS 設計之所以採用這些先進製程,是因為只有這些製程具備足夠的整合密度,能在大型設計中建構數百萬顆電晶體。

第三,Ansys 已將許多核心演算法轉移到現代化、雲端最佳化的資料基礎架構中,並應用大數據分析技術於電子模擬。透過天然分散的資料組織架構,像 Totem-SC 這類的類比電源完整性工具能在雲端運行,利用 250 個運算核心在 24 小時內完成對 HBM4 堆疊中八顆記憶體晶片的分析。這遠遠超越傳統類比 EDA 工具的能力,並為處於 AMS 設計前沿的工程師提供急需的模擬能力。

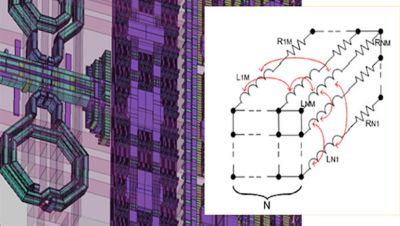

要準確捕捉高速訊號的行為,需要對互連進行完整電磁分析,包括寄生電感 (L)、寄生電阻 (R) 與寄生電容 (C)。

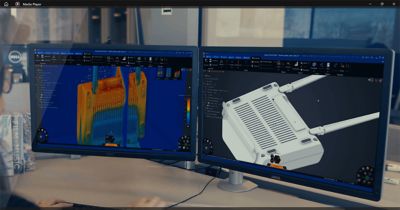

利用 HFSS 軟體搭配網格融合技術,進行完整晶片封裝與連接器的類比模擬。網格融合技術能大幅提升 HFSS 軟體的速度與容量,且不影響準確度。

以模擬應對高容量挑戰

利用更先進製程節點設計日益龐大的 AMS 電路,這一趨勢已延伸至嵌入式記憶體、HBM、影像感測器、FPGA 與 3D-IC 中介層等產品。傳統類比設計工具既缺乏所需的資料基礎架構,也沒有足夠的演算法效能來分析如此龐大的設計。面對這項挑戰,Ansys 的高容量設計軟體工具讓類比工程師能精確模擬業界部分最大型的 AMS 設計行為,並如期、依規格交付高效能產品。

下載《以多物理最佳化類比設計》電子書,深入瞭解如何利用 Ansys 解決方案克服您的類比設計挑戰。