現代裝置及其元件的快速發展無庸置疑,但工程師們又是如何因應這些發展以跟上腳步的呢?設計類比與混合訊號 (AMS) 半導體電路既是一門科學,也是一門藝術。展望未來,這些技術進展將為工程師帶來令人振奮的挑戰與機會,突破創造力與技術專業的極限。

在半導體工程中,電磁場與矽之間複雜的非線性交互作用難以預測,而當製程技術進展至 16 奈米及更小節點時,由這些交互作用所帶來的挑戰也隨之急劇增加。瞭解這些挑戰存在的原因,以及設計人員在先進節點下要如何可靠地進行類比電路設計,可說是極其重要。

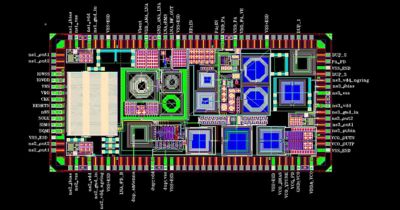

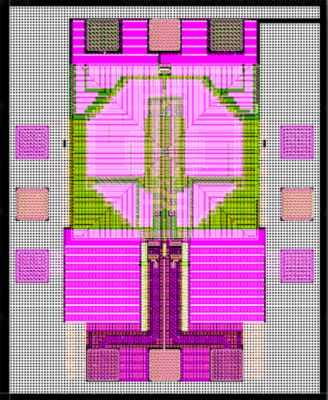

電壓控制振盪器 (VCO) 的佈局範例是一種常見於多數數位 IC 的類比結構。

寄生效應如何影響晶片製造

自半導體產業發展初期以來,透過建模與模擬類比效應來進行精確預測,一再證明是極具價值的作法。SPICE 電路模擬器是半導體工程師廣泛使用的工具,也是所有類比晶片設計的基礎工具。然而,類比設計仍仰賴一定程度的專業知識與工程判斷,這兩者對成功與否至關重要。

SPICE 模擬的準確度取決於所提供的電路模型,因為真實世界中的效應與交互作用難以重現。晶體管元件必須經過極為謹慎與細緻的特性建模,其結果會納入由半導體晶圓代工廠提供的製程設計套件 (PDK) 資料庫。然而,晶片內部的互連寄生效應模型必須能夠在每次佈局迭代時快速且簡便地提取,因為隨著製程節點縮小與操作頻率提升,這些寄生效應對電路效能的影響也愈加顯著。互連寄生效應對電路效能的影響已強烈到需要精確建模電磁、射頻 (RF)、熱、光學、寄生效應、電壓降、可靠度、功率及其他多物理,才能確保設計的成功。

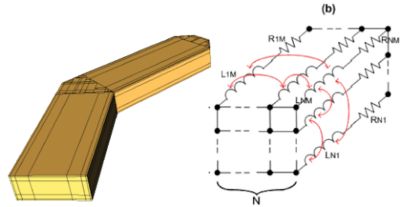

來自 Ansys RaptorX 軟體的一段半導體互連及其提取的電磁模型,包含完整的電感耦合。有限元素網格會自動建立,以呈現模擬器的實體佈局。

因此,多數類比設計團隊會選擇使用成熟製程節點,藉此避開採用先進矽製程所帶來的設計挑戰。先進矽製程不僅製造成本高昂,而且其優勢主要集中於數位設計。諸如整合密度與切換速度等標準,通常優先於類比設計所關注的線性行為與可預測交互作用。如有選擇空間,多數類比設計工程師傾向避開最新的鰭式場效電晶體 (finFET) 與閘極全環 (GAA) 電晶體技術,因為這些技術會增加設計工作的困難度。在這些節點下的電氣行為變得更難以預測,且更容易受到周圍元件的干擾。此外,在功耗降低與整合密度提升方面的優勢,對類比設計的關聯性並不高。

需要電磁建模以求準確度

針對將所有電子元件整合至單一先進節點晶片的大型系統單晶片 (SoC) 元件而言,類比設計使用先進節點已無可避免。這在半導體設計領域已經是數十年的有利趨勢。因此,每顆 SoC 中都會包含一些類比子電路,而這些子電路會與其他設計部分共用相同的先進製程技術。此外,因應市場趨勢,如整合感測需求、無線通訊 (例如 WiFi、藍牙與 5G) 以及對視訊與觸控螢幕的高度依賴,先進節點晶片上的類比內容也不斷增加。為了成功完成設計,類比工程師需要電磁模擬器,來提取 SoC 類比互連的精確電阻、電感與電容 (RLC) 或 S 參數模型。

Intel 的先進矽製程技術包括 RibbonFET 閘極全環電晶體與 PowerVia 技術,該技術將電源分配網路從晶片正面移至背面。這些創新技術雖能縮小晶片尺寸、提升效能並降低電壓損失,卻也帶來全新的多物理分析挑戰。

你知道嗎?

所有電子裝置中至少含有一個 (通常是多個) 由矽製成的積體電路 (IC),也就是我們常說的晶片。類比與混合訊號 (AMS) 晶片的應用日益增加,因為它們能在單一晶片設計中無縫整合類比與數位訊號。AMS 晶片確保類比電路與數位處理器之間的順暢溝通,對於行動與無線裝置、電動車 (EV)、物聯網 (IoT) 網路等應用而言,扮演了關鍵角色。

工程師在送交設計至矽晶圓代工廠 (即所謂的「晶圓廠」) 製造之前,會利用基於物理的模擬軟體對其 IC 進行詳細模擬。製造一批晶片可能需要三到四個月的時間,以及數百萬美元的成本,而且一旦出錯也無法修復或更改。因此,設計人員必須藉由模擬軟體等工具,在進入製造流程之前確保晶片能夠正確運作,這點至關重要。

採用先進製程節點的電路佈局會引入許多物理效應,對於準確的電磁分析形成重大挑戰。更小的幾何尺寸導致元件間物理距離更近、電磁耦合更強,以及電阻更高,這些因素會使類比電路的效能對於物理佈局中的細節更加敏感。

瞭解佈局依賴效應

更重要的是,有大量製程效應使得在先進節點中使用傳統建模技術變得更加困難。這些效應統稱為佈局依賴效應 (Layout-dependent effects;LDE)。LDE 效應如蝕刻、多重圖樣、貼合電介質、損傷與負載,皆必須透過解析方式進行計算,才能產生準確的電磁模型。然而,許多傳統的電磁建模工具並不支援 LDE,並可能在先進節點中產生不準確的結果。基準測試顯示,忽略先進的 LDE 可能導致極大的模型誤差,例如串聯電阻的測量結果可能偏差高達 140%,總電容的偏差則可達 25%。

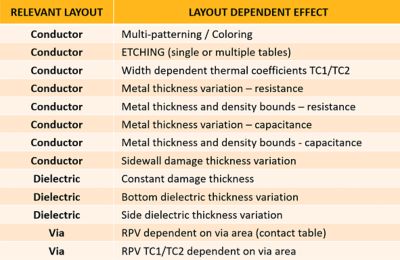

概述會影響先進製程節點半導體電路電氣行為的佈局依賴效應 (LDE) 。

上述表格更完整地列出常見的 LDE 清單。這說明了蝕刻與平坦化等製程步驟如何導致導體、電介質與通孔在電氣與熱特性上產生變化。例如,在某些應用中,若將三種電介質效應全部納入考量,總電容可能會增加 10%。這凸顯出設計人員準確考慮 LDE 的重要性。

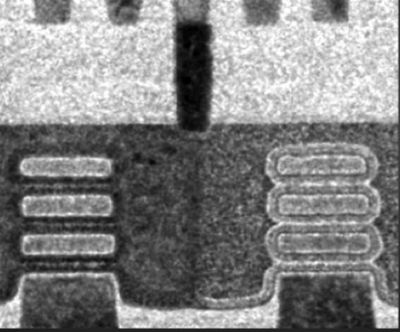

由台積電製造的先進奈米片電晶體結構展現了佈局依賴效應 (LDE),這些效應在進行類比電路精確分析時必須納入考量。圖片由台積電提供

先進製程節點的解決方案

Ansys 與領先的晶圓代工廠合作,推出專為先進節點 LDE 最佳化的 Ansys RaptorX 電磁求解器。RaptorX 求解器可完整建模所有先進互補式金屬氧化物半導體 (CMOS) 製程節點中 2 奈米及以下的佈局依賴效應。RaptorX 軟體可透過加密的 PDK 讀取特定製程節點的 LDE 參數,同時保護晶圓代工廠的智慧財產權 (IP)。

準確考量先進製程節點效應與 LDE 可大幅提升模擬的準確度與可靠度。像 RaptorX 這類先進的模擬引擎,讓設計人員能夠在 SoC 中設計高速類比元件,並充分發揮最新矽製程節點的優勢。將這些效應納入 RaptorX 計算為自動進行的操作,無需變更既有的參數擷取流程。

下載《以多物理最佳化類比設計》電子書,並造訪 Ansys 網站,深入瞭解Ansys 半導體產品系列。