Leading in Power Integrity Signoff with Breakthrough Innovation

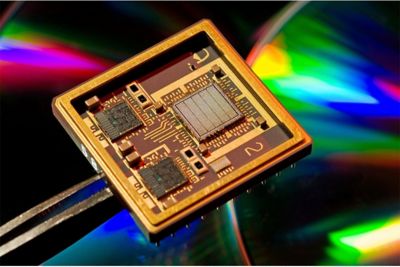

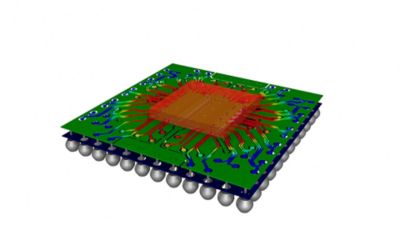

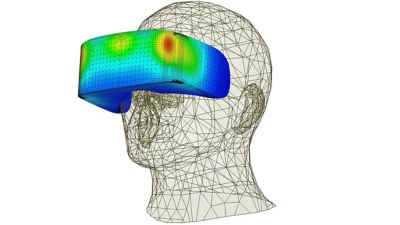

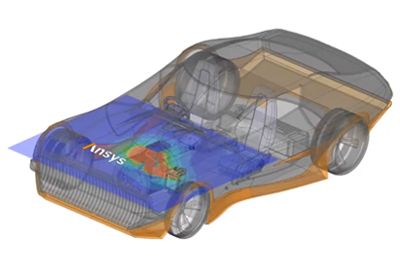

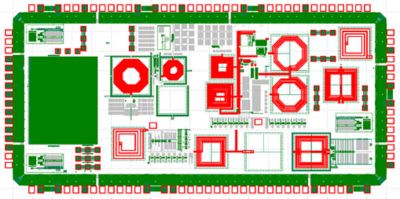

Ansys delivers the industry’s broadest range of foundry-certified golden signoff tools for semiconductor, electronic, and complete system design, including the latest 2nm nodes.

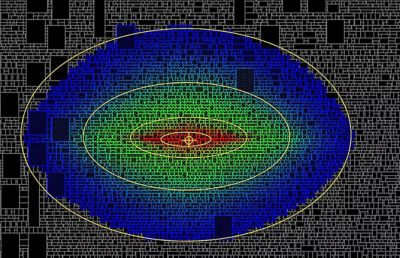

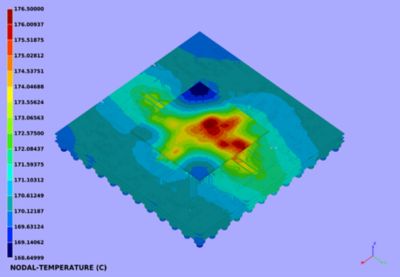

Stop by our booth to learn how our new SigmaDVD technology radically changes how leading customers analyze dynamic voltage drops.

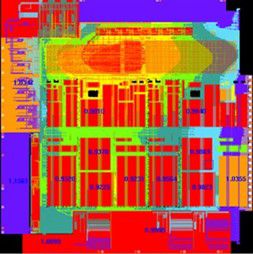

See how the latest IR-ECO and IR-STA joint developments have integrated the industry’s best signoff engines, PrimeTime(tm) and RedHawk-SC(tm).