-

-

학생용 무료 소프트웨어에 액세스하기

차세대 엔지니어에게 힘을 실어주는 Ansys

학생들은 세계적 수준의 시뮬레이션 소프트웨어를 무료로 이용할 수 있습니다.

-

지금 바로 Ansys에 연결하십시오!

미래를 설계하기

시뮬레이션이 다음 혁신을 어떻게 지원할 수 있는지 알아보려면 Ansys와 연결하십시오.

국가

무료 트라이얼

제품 및 서비스

학습하기

회사 정보

Back

제품 및 서비스

초대형 아날로그 및 혼합 신호 칩은 단일 반도체 칩에 아날로그 및 디지털 구성 요소를 원활하게 결합하는 첨단 집적 회로(IC)입니다. 이러한 혁신적인 혼합 신호 IC는 두 요소 간의 원활한 상호작용을 촉진하여 전반적인 칩 성능 및 기능을 크게 향상합니다.

대부분의 아날로그 및 혼합 신호(AMS) 반도체 설계는 현재 AI 및 그래픽 처리를 위해 제조되고 있는 대형 디지털 칩과 비교했을 때 상대적으로 작습니다. 디지털 칩은 단일 칩에 10억 개가 넘는 트랜지스터를 포함하도록 쉽게 확장할 수 있지만, AMS 칩에는 흔히 수천 개만 들어 있습니다. 이러한 불일치의 이유는 아날로그 회로 동작에 영향을 미치는 복잡한 다중물리 상호작용에서 비롯됩니다.

아날로그 효과는 흔히 매우 비선형적이며 물리적 레이아웃의 정밀한 세부 사항에 극도로 민감합니다. 인덕턴스와 같은 중요한 전기 파라미터는 칩에서 멀리 떨어진 전류 흐름에 의해서도 영향받을 수 있습니다. 시뮬레이션 툴은 물론 칩 엔지니어는 이러한 복잡성을 시뮬레이션하고 이해하는 데 어려움을 겪고 있으며, 이로 인해 아날로그 회로의 크기가 자연스럽게 제한됩니다.

아날로그 엔지니어는 전자 설계 자동화(EDA) 소프트웨어 툴을 사용하여 해당 칩을 설계하지만, 이러한 툴도 일반적으로 기능에 한계가 있습니다. 이는 전자기 분석과 같은 아날로그 시뮬레이션 엔진을 일정 수준 이상으로 확장하는 것이 어렵기 때문입니다.

3D 스택에 12개의 메모리가 있는 SK하이닉스의 HBM3 고대역폭 메모리. 사진 제공: SK하이닉스

아날로그 솔루션의 필요성을 촉진하는 첨단 제조

AMS 환경은 지난 몇 년 동안 많은 진화를 거쳐 왔으며, 이로 인해 완전한 아날로그 분석이 필요한 상당히 큰 반도체 장치가 등장하게 되었습니다. 이러한 예로는 HBM4와 같은 고대역폭 메모리(HBM), 첨단 제조 노드의 FPGA(Field-Programmable Gate Array), CMOS(Complementary Metal-Oxide-Semiconductor) 이미지 센서(CIS)가 있습니다. 또한 반도체 산업 전체가 2.5D(병렬형) 및 3D(적층형) 멀티 다이 어셈블리 기술을 받아들이고 있습니다. 이 거대한 반도체 시스템에 있는 12개 이상의 칩은 인터포저라고 하는 대형 연결 기판을 통해 함께 연결됩니다.

고대역폭 메모리 모듈(HBM)이 집적된 AMD의 VERSAL FPGA(Field-Programmable Gate Array). 사진 제공: AMD

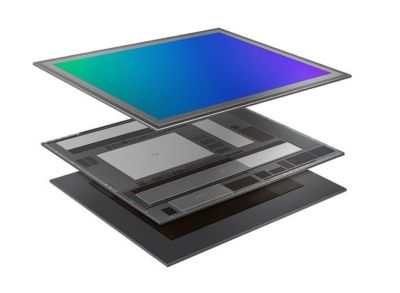

이러한 설계 중 다수는 이름만 디지털이지만, 실제로는 신뢰할 만한 성공을 달성하기 위해 광범위한 아날로그 시뮬레이션이 필요할 수 있습니다. 또한 크기가 매우 큽니다. 고성능 컴퓨팅(HPC) 응용 분야에 일반적으로 사용되는 HBM4 메모리 모듈에는 640억 개가 넘는 트랜지스터가 있습니다. 저용량 산업 응용 분야에 사용되는 가장 큰 FPGA에는 400억 개가 넘는 트랜지스터가 포함되어 있습니다. 디지털 카메라 및 스마트폰에 사용되는 CMOS 이미지 센서는 시장에서 가장 진보된 3D-IC 다중물리 스택 중 일부이며 1,000만 개가 넘는 픽셀을 포함하고 있습니다. 그리고 3D-IC 어셈블리의 많은 칩을 연결하는 인터포저에는 수백만 개의 신호 라인이 포함되어 있습니다.

데이터 처리 칩 위에 적층된 이미지 감지 칩을 보여주는 삼성의 ISOCELL CMOS 이미지 센서(CIS). 사진 제공: 삼성

이러한 진화의 이유는 강력한 시장 동향에 근거를 두고 있습니다. 첨단 제조 노드는 매우 높은 주파수의 디지털 신호를 가능하게 하지만 이로 인해 아날로그 설계에는 새로운 과제가 제기됩니다. 전통적인 저항-커패시턴스(RC) 모델링으로는 정확하게 시뮬레이션할 수 없기 때문입니다. 이러한 속도에서는 인덕턴스(L) 및 차폐 금속을 포함한 전체 전자기 모델링이 필수적이며, 이를 위해서는 아날로그 시뮬레이션 툴이 필요합니다.

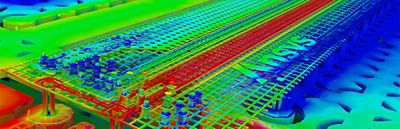

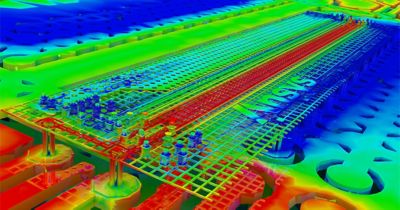

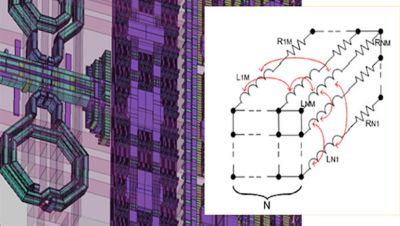

3D-IC 멀티 다이 어셈블리를 위한 인터포저의 Ansys HFSS 전자기 시뮬레이션 결과

영향력이 큰 또 다른 동향은 오늘날의 장치에서 비디오가 널리 사용되면서 고화질 이미지 센서의 중요성이 커졌다는 것입니다. 또한 이러한 장치는 아날로그 분석에 의존하여 광학 응용 분야, 디지털 이미징에 사용되는 CCD(Charge-Coupled Devices), 고속 입출력(IO)을 지원합니다. FPGA에서 사용할 수 있는 프로그래밍 가능한 로직 및 고속 연결은 아날로그 툴로 분석되는 명목상 디지털 회로의 예이기도 합니다. 임베디드 메모리, HBM, CIS, FPGA는 모두 기존 AMS 칩의 크기를 훨씬 초과하는 수백만 개의 트랜지스터를 탑재한 대규모 설계입니다.

아날로그 설계의 새로운 시대를 위한 새로운 툴

대형 회로의 설계자에게는 첨단 노드를 사용하는 고속의 아날로그 동작을 안정적으로 예측할 수 있는 차세대 아날로그 툴이 필요합니다. 이전의 전통적인 방법은 작은 하위 섹션만 분석했지만, 이러한 대규모 설계에는 신뢰할 수 있는 정확도를 위해 전체 칩 시뮬레이션이 필요합니다. Ansys는 이러한 과제를 해결하는 툴과 기술을 개발하기 위해 세계적인 수준의 실리콘 공급업체들과 긴밀하게 협력해 왔습니다.

첫 번째 기술은 기본 시뮬레이션 알고리즘의 속도와 용량을 획기적으로 증가시키는 것을 포함합니다. Ansys HFSS 칩-시스템 전자기 시뮬레이션 플랫폼 및 Ansys RaptorX 실리콘 최적화 전자기 솔버와 같이 널리 사용되는 전자기 툴은 이제 정교한 메시 융합 기술을 갖추고 있어 정확도가 떨어지지 않고 단일 패스에서 수백 개의 연결 포트가 있는 대형 모델을 신속하게 시뮬레이션합니다.

설계자들이 직면한 또 다른 새로운 아날로그 과제는 3D-IC의 여러 연결된 칩에 걸친 정전기 방전(ESD) 회로를 검증하는 것입니다. Ansys는 대형 IP 및 3D-IC를 위한 Ansys PathFinder-SC 정전기 방전 신뢰성 사인오프 플랫폼을 개발했으며, 이는 TSMC 파운드리에 의해 멀티 다이 ESD 사인오프 솔루션으로 인증되었습니다. 설계가 커짐에 따라 전력 무결성 및 전압 강하 분석도 점점 더 계산 집약적이 되고 있습니다. 대규모 아날로그, 혼합 신호 및 3D-IC를 위한 Ansys Totem-SC 전력 무결성 사인오프 플랫폼은 초대형 AMS 설계를 위한 특성화된 설계 솔루션입니다.

둘째, Ansys는 주요 파운드리와 긴밀하게 협력하여 10nm 이하의 첨단 finFET 노드로 설계할 때 나타나는 레이아웃 종속 효과(LDE)를 완벽하게 지원합니다. 이는 LDE로 인해 25% 이상의 편차를 나타낼 수 있는 이러한 첨단 노드에서 커패시턴스와 인덕턴스를 정확하게 예측하는 데 필수적입니다. 대규모 AMS 설계는 이러한 첨단 공정을 통해 제조됩니다. 대규모 설계에서 수백만 개의 트랜지스터를 만드는 데 필요한 집적도를 갖춘 유일한 공정이기 때문입니다.

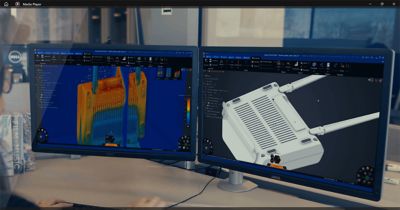

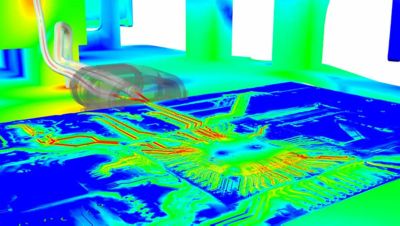

셋째, Ansys는 핵심 알고리즘 중 많은 부분을 전자 시뮬레이션에 빅데이터 분석 기법을 사용하는 최신 클라우드 최적화 데이터 인프라로 전환했습니다. 자연스럽게 분산된 데이터 구성을 통해 클라우드에서 Totem-SC 소프트웨어와 같은 아날로그 전력 무결성 툴을 실행하여 250개의 컴퓨팅 코어를 사용해 24시간 이내에 HBM4 스택의 메모리 칩 8개를 분석할 수 있습니다. 이는 레거시 아날로그 EDA 툴의 기능을 근본적으로 뛰어넘으며, AMS 설계의 최첨단에서 작업하는 설계 엔지니어에게 매우 필요한 시뮬레이션 기능을 제공합니다.

고속 신호의 동작을 정확하게 포착하려면 기생 인덕턴스(L)는 물론 기생 저항(R) 및 커패시턴스(C)를 포함한 상호 연결의 전체 전자기 분석이 필요합니다.

메시 융합 기술을 사용하는 HFSS 소프트웨어를 통한 전체 칩 패키지 및 커넥터의 아날로그 시뮬레이션. 메시 융합은 정확도에 영향을 주지 않으면서 HFSS 소프트웨어의 속도와 용량을 근본적으로 증가시킵니다.

시뮬레이션으로 고용량 과제 해결

임베디드 메모리, HBM, 이미지 센서, FPGA 및 3D-IC 인터포저와 같은 제품에서 점점 더 큰 AMS 회로를 설계하기 위해 더욱 진보된 노드를 사용하는 추세는 계속됩니다. 기존의 아날로그 설계 툴은 이러한 대규모 설계를 분석하는 데 필요한 데이터 인프라도, 알고리즘 성능도 제공하지 못했습니다. 이러한 과제에 발맞춰 아날로그 엔지니어는 Ansys의 고용량 설계 소프트웨어 툴을 사용하여 업계에서 가장 큰 AMS 설계의 동작을 정확하게 시뮬레이션함으로써 일정과 사양에 맞춰 고성능 제품을 제공할 수 있습니다.

다중물리를 사용한 아날로그 설계 최적화 전자책을 다운로드하고 Ansys 솔루션을 사용하여 아날로그 설계 과제를 해결하는 방법에 대해 자세히 알아보십시오.

Advantage 블로그

Ansys 및 다른 기술 전문가의 기고문을 제공하는 Ansys Advantage 블로그에서는 Ansys 시뮬레이션이 인간의 발전을 촉진하는 혁신을 어떻게 지원하는지에 대한 최신 소식을 계속해서 전해 드립니다.