ホワイトペーパー

3D異種チップ集積: 設計と検証に関する課題

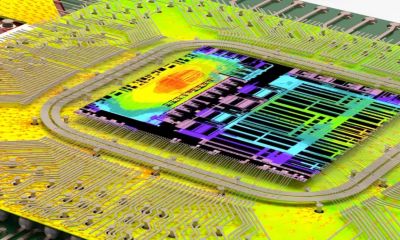

次世代半導体製品では、システムの高密度化、高速化、歩留まりの向上を図るために垂直統合技術の導入が進んでいます。複数の物理特性にまたがる結合効果が増加したため、これらの現象のコシミュレーションや協調解析は、ロバストなチップ-パッケージ-システムの設計に不可欠です。最先端の2.5D/3D-ICシステムは、複数のダイ、インターポーザー、パッケージング層、接続基板で構成されており、結合効果はより一層困難な課題となっています。異なるプロセス技術による異なる電気特性を持つチップレット集積を集積するマルチダイ異種チップ集積(HI: Heterogeneous Integration)の登場により、既存の設計ツールやフローでは不十分であり、追加の設計および検証機能が必要になっています。システムインパッケージ(SiP)から、インターポーザーを活用した先端パッケージングによる2.5D-IC、さらにはスタックダイ/チップレット集積を使用した真の3D-ICまで、信号ネットと電源ネットワークの両方のインターコネクトアーキテクチャが新たに登場したことで、超大容量データと拡張性に優れたコンピューティングテクノロジーを備えた革新的な電子設計自動化(EDA)ソリューションが必要になります。