Safe & Secure Systems

Dramatically decrease analysis efforts with efficient application of quality, safety, reliability and cybersecurity analysis methods at the system, item, software, hardware and PCB levels.

Ansys empowers the next generation of engineers

Students get free access to world-class simulation software.

Design your future

Connect with Ansys to explore how simulation can power your next breakthrough.

Students get free access to world-class simulation software.

Connect with Ansys to explore how simulation can power your next breakthrough.

Dramatically decrease analysis efforts with efficient application of quality, safety, reliability and cybersecurity analysis methods at the system, item, software, hardware and PCB levels.

High Level Features

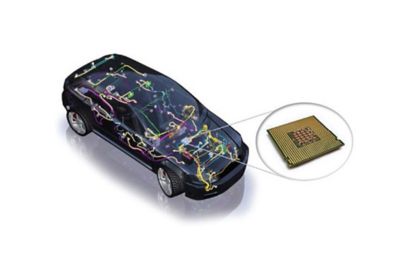

Ansys safety & cybersecurity threat analysis software facilitates model-based safety analysis, safety concept creation, safety management and cybersecurity assessment for safety-critical electrical and electronic (E/E) and software (SW) controlled systems.

Using this software, engineers can deliver safe and secure products, reduce time to market, maximize profit margins and comply with standards like ISO 26262, IEC 61508, ARP 4754A/ARP 4761, ISO 21448 and ISO 21434.

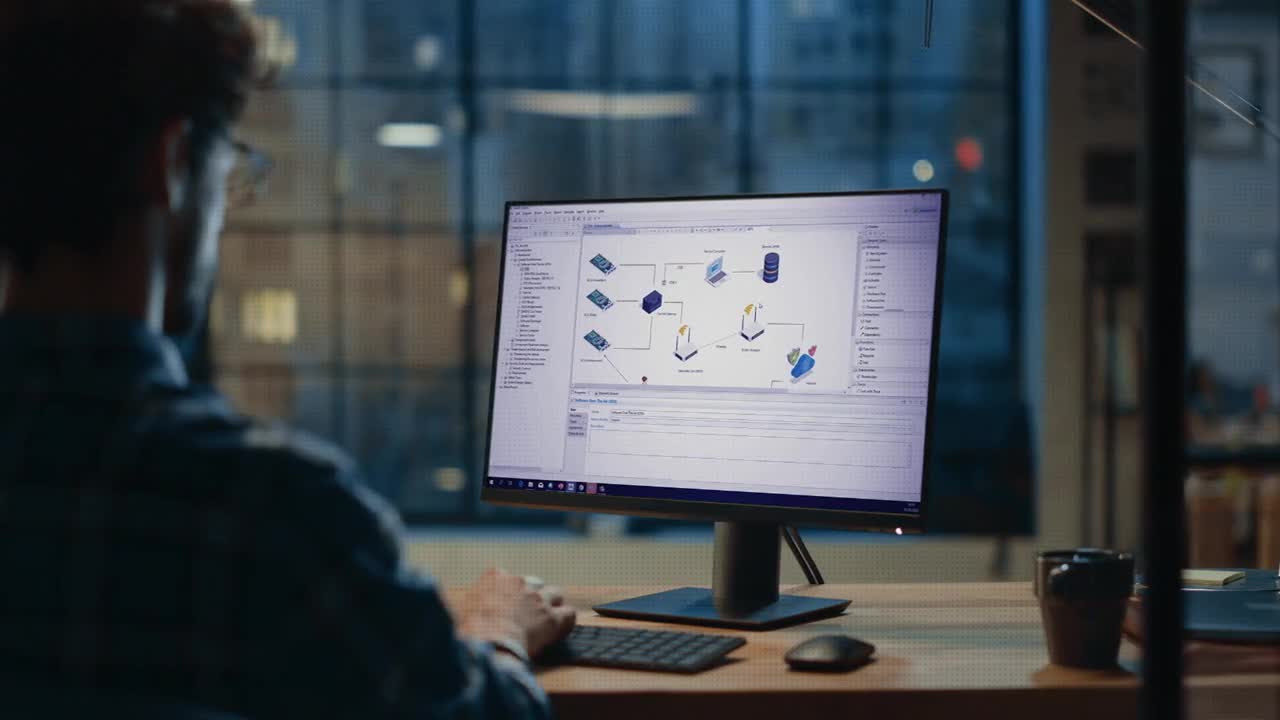

Dramatically decrease safety analysis for electronically-controlled safety related functions and accelerate time to market with state-of-the-art methods in the model-based environment of Ansys medini analyze.

March 2026

The 2026 R1 introduces bidirectional interoperability between medini analyze and VC FSM, enabling an end-to-end safety workflow between the system and silicon. Major PLM integrations are extended in this release, including Cameo, Codebeamer, DOORS Classic, and Jama.

The new Ansys Engineering Copilot provides intelligent assistance and centralized resources, enabling AI-powered support and easy access to major knowledge bases.

The Ansys Safety Analysis software suite streamlines safety and security analysis, decreasing efforts and costs.

Ansys medini analyze for Cybersecurity delivers an easy-to-use modeling and analysis tool that ensures your electronics architecture — across its many connections and interfaces — is impervious to external attacks. Watch this impactful video to understand how you can replace your outdated tools and manual processes with the speed and automation of medini analyze to deliver safe and secure products, reduce time to market, maximize profit margins and comply with upcoming regulations surrounding cybersecurity.

Dramatically decrease safety analysis for electronically-controlled safety related functions and accelerate time to market with state-of-the-art methods in the model-based environment of Ansys medini analyze.

Safety is a crucial property for many products, especially in the aerospace and defense industry, essential to obtaining the necessary certification. To identify appropriate safety requirements early in the development process and to be able to demonstrate their fulfillment by design, safety analysis must be well integrated into the system development process in all phases. In a model-based approach that is usually highly iterative, it's a great benefit to base the safety analysis on models. This allows us to deal with changes quickly and always have up-to-date analysis to guide development decisions.

If you're facing engineering challenges, our team is here to assist. With a wealth of experience and a commitment to innovation, we invite you to reach out to us. Let's collaborate to turn your engineering obstacles into opportunities for growth and success. Contact us today to start the conversation.