-

-

Access Free Student Software

Ansys empowers the next generation of engineers

Students get free access to world-class simulation software.

-

Connect with Ansys Now!

Design your future

Connect with Ansys to explore how simulation can power your next breakthrough.

Countries & Regions

Free Trials

Products & Services

Learn

About

Back

Products & Services

Back

Learn

Ansys empowers the next generation of engineers

Students get free access to world-class simulation software.

Back

About

Design your future

Connect with Ansys to explore how simulation can power your next breakthrough.

Free Trials

ANSYS BLOG

October 4, 2019

Simulating Automotive ICs for AEC-Q100/ISO 26262 Qualification

Automotive chip designers are incorporating an abundance of semiconductors into their designs to accommodate advanced driver assistance systems (ADAS), fully autonomous vehicles, electric vehicles (EVs), connectivity and security.

As a result, designers are challenged to ensure that the semiconductors driving these systems meet strict automotive safety standards, such as:

Autonomous vehicles will increasingly rely on semiconductors to see, think, drive, learn and repeat.

- ISO 26262: Road Vehicle — Functional Safety

- AEC-Q100: Failure mechanism Based Stress Test Qualification for Integrated Circuits

Differentiated semiconductors are set to revolutionize mobility because they drive the implementation of electronics and integrated circuits (ICs) that are essential to the development of ADAS and autonomous cars. These electronics include:

- Image sensors/radars/lidars

- Vision processors

- Signal processors

- Artificial intelligence (AI)

- Connectivity solutions

- Hard-coded security features

The system-on-chips (SoCs) used in these safety critical systems involve advanced multicore designs with high levels of integration, functionality and operating speeds. It’s not uncommon to find heterogenous dies integrated within the same packages (in 2.5D/3D-IC configurations) to offer superior performance and power metrics.

Chip designers can use simulation to ensure that semiconductor intellectual properties (IPs), SoCs and system-in-packages (SiPs) all meet the automotive electronics functional safety and reliability requirements of ISO 26262 and AEC-Q100.

What Are AEC-Q100 and ISO 26262?

The ISO 26262 and AEC-Q100 requirements for semiconductors are strict because chip designers need to ensure that ADAS and autonomous vehicle systems are functionally safe under various conditions.

To achieve ISO 26262 certification, all road vehicle electronics systems need to pass functional safety requirements at every development phase — from concept to productization.

Autonomous vehicles will need semiconductors that can meet ISO 26262 and AEC-Q100 safety standards.

To achieve AEC-Q100 certification, ICs must go through rigorous failure mechanism stress tests and qualifications. These parts must pass these reliability requirements to meet different automotive grade levels.

For instance, a car in the hot summers of Las Vegas must be as safe as a car in a Canadian winter. As a result, all components must pass electrostatic discharge (ESD) and thermal stress tests to ensure they will operate in these, and other conditions.

Additionally, cars typically operate for 10 to 15 years. As a result, chip designers need to demonstrate that autonomous and ADAS systems have a zero-failure rate during the course of a car’s operation.

To ensure ADAS and autonomous systems endure the mechanical and thermal stress over the life of the car, chip designers need to design enough redundancies into the system to account for any conceivable failure mode. One of the best ways to ensure this level of semiconductor quality is to ensure automotive ICs are certified to AEC-Q100 and ISO 26262 standards.

Quality has always been key for automotive electronics systems, but auto chip designers need to keep up with the rapid pace of innovation in the industry. For this reason, the technologies that brought about innovation in the mobile semiconductor market — such as advanced fin field effect transistors (FinFETs) and packaging technologies — are being adopted into the automotive semiconductor market.

Simulation Challenges to Meet ISO 26262 and AEC-Q100 Automotive IC Requirements

The simulation challenges to ensure that FinFET designs and 2.5D/3D-IC advanced packaging technologies meet ISO 26262 and AEC-Q100 standards are complex because they require the use of multiphysics simulations.

For instance, autonomous systems need to be power-efficient. Otherwise, the car’s battery drains quickly — affecting mileage. Power reduction techniques like clock and data gating can maximize power efficiency, particularly when addressed early in the design cycle.

Ansys PowerArtist enables chip designers to improve the power efficiency of automotive ICs.

However, certain power reduction techniques, like power gating, may not be viable for automotive systems. Think of it: The time it takes for the system to wake up from its power gated sleep-state can be catastrophic in collision avoidance scenarios.

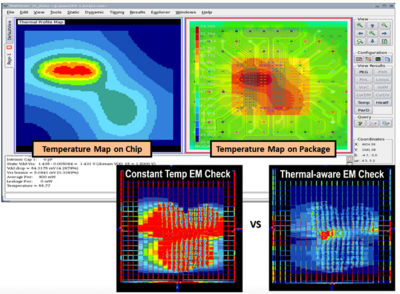

Example of thermal-aware electromigration (EM) analysis for filtering EM hotspots that need to be fixed

Another multiphysics challenge relates to how power impacts the thermal signature of a chip. Thermal effects can lead to long-term reliability issues, therefore, lowering the supply’s voltage is beneficial because it reduces the overall power profile. However, this results in reduced headroom affecting the power supply’s noise and variability, ultimately impacting the timing of the chip.

The relationship between power, noise and high-speed switching in signal lines is exacerbated by electromagnetic crosstalk. This can lead to functional failures, reduced mean time to failure or reduced performance of the product.

Chip designers can use Ansys’ semiconductor portfolio to deal with all of these multiphysics challenges to meet the stringent safety and reliability of automotive electronics systems.

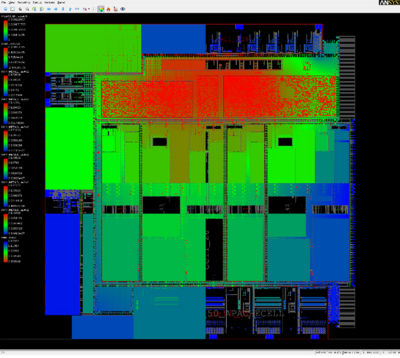

Example of a RedHawk-SC voltage drop map that is used to detect power integrity issues that impact timing

Ansys Semiconductor Portfolio Meets ISO 26262 Certification

To meet ISO 26262 standards, chip designers need electronic design automation (EDA) tools that are certified within the ISO 26262 “Tool Confidence Level 1” (TCL1) category.

This certification ensures that the tools will not introduce errors into the design that will compromise the functional safety of the overall system. As a result, chip designers can ensure the safety of their electronic systems by understanding the EDA tool, including:

- Usage models

- Interactions with downstream tools

- Potential malfunctions or erroneous reporting

- Error detection and prevention methods

The Ansys semiconductor portfolio for power efficiency, power integrity and reliability has achieved ISO 26262 TCL1 certification. This certification enables automotive IC designers to meet rigorous safety requirements for ADAS and autonomous applications.

Auto chip designers can leverage Ansys PowerArtist, Ansys Totem and the Ansys RedHawk family of multiphysics simulations for all ISO 26262 safety-related development projects at any automotive safety integrity level (ASIL).

Ansys provides comprehensive multiphysics simulations to accurately model power, thermal, reliability and electromagnetic effects across chips, packages and systems to capture various failure mechanisms.

Chip makers can use Ansys multiphysics simulations to ensure semiconductors meet the stringent safety and reliability requirements for ISO 26262 and AEC-Q100.

To learn more, check out the press release about Ansys and TSMC’s Automotive Reliability Solution Guide 2.0