-

-

Accédez au logiciel étudiant gratuit

Ansys donne les moyens à la prochaine génération d'ingénieurs

Les étudiants ont accès gratuitement à un logiciel de simulation de classe mondiale.

-

Connectez-vous avec Ansys maintenant !

Concevez votre avenir

Connectez-vous à Ansys pour découvrir comment la simulation peut alimenter votre prochaine percée.

Pays et régions

Espace client

Support

Communautés partenaires

Contacter le service commercial

Pour les États-Unis et le Canada

S'inscrire

Essais gratuits

Produits & Services

Apprendre

À propos d'Ansys

Back

Produits & Services

Back

Apprendre

Ansys donne les moyens à la prochaine génération d'ingénieurs

Les étudiants ont accès gratuitement à un logiciel de simulation de classe mondiale.

Back

À propos d'Ansys

Concevez votre avenir

Connectez-vous à Ansys pour découvrir comment la simulation peut alimenter votre prochaine percée.

Espace client

Support

Communautés partenaires

Contacter le service commercial

Pour les États-Unis et le Canada

S'inscrire

Essais gratuits

DATE: 10/28/2022

PRESS RELEASE

Ansys Multiphysics Solutions Achieve Certification for TSMC N4 Process and TSMC FINFLEX™ Architecture

Ansys is certified for TSMC’s innovative FINFLEX™ architecture on N3E for flexible power/performance tradeoffs

Key Highlights

- Ansys® Redhawk-SC™ and Ansys® Totem™ power integrity platforms are certified for TSMC’s FinFlex™ architecture on N3E

- The certification also extends to the TSMC N4 process technology

PITTSBURGH, PA, October 28, 2022 – Ansys (NASDAQ: ANSS) and TSMC continued their long-standing technology collaboration to announce certification of Ansys’ power integrity software for TSMC’s FINFLEX™ innovation as well as the TSMC N4 process. TSMC’s FINFLEX™ architecture allows Ansys RedHawk-SC and Totem customers to make fine-grained speed-power tradeoffs which reduce a chip’s power footprint without sacrificing performance. This is important for lowering the environmental impact of many semiconductor applications, including machine learning, 5G mobile, and high-performance computing (HPC). This latest collaboration builds on the recent certification of the Ansys platform for TSMC’s N3E process.

“The unparalleled flexibility of our FINFLEX™ innovation provides tremendous chip design advantage and flexibility to optimize for high performance, low power, or a balance between the two,” said Dan Kochpatcharin, head of Design Infrastructure Management Division at TSMC. “Our latest collaboration with Ansys on TSMC’s 3nm technology makes it easy for our mutual customers to take advantage of FINFLEX's benefits with full confidence in the power integrity and reliability signoff verification results from RedHawk-SC and Totem.”

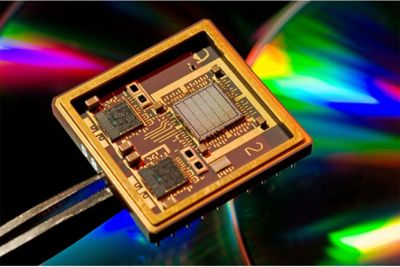

Chip image TSMC’s FINFLEX™ architecture allows Ansys RedHawk-SC and Totem customers to make fine-grained speed-power tradeoffs, reducing a chip’s power footprint without sacrificing performance

Based on TSMC’s N3E process technology, TSMC FINFLEX architecture allows chip designers to choose from three options of FIN configurations for each standard cell implementation: One for highest performance and fastest clock frequencies, one for balanced efficient performance, and an ultra-power efficiency for the lowest leakage and highest density. This combination of characteristics enables chip designers to choose the best speed-performance option for each of the key functional blocks on a chip using the same design toolset.

"Ansys has developed an integrated software platform of multiphysics simulation and analysis tools with an emphasis on power management to minimize the design and operating costs of semiconductors," said John Lee, vice president and general manager of the electronics, semiconductor and optics business unit at Ansys. “Our ongoing collaboration with TSMC aligns with our efforts to enable a sustainable technology future, enabling mutual customers to improve chip performance while reducing power consumption."

About Ansys

When visionary companies need to know how their world-changing ideas will perform, they close the gap between design and reality with Ansys simulation. For more than 50 years, Ansys software has enabled innovators across industries to push boundaries by using the predictive power of simulation. From sustainable transportation to advanced semiconductors, from satellite systems to life-saving medical devices, the next great leaps in human advancement will be powered by Ansys.

Take a leap of certainty … with Ansys.

Ansys and any and all ANSYS, Inc. brand, product, service and feature names, logos and slogans are registered trademarks or trademarks of ANSYS, Inc. or its subsidiaries in the United States or other countries. All other brand, product, service and feature names or trademarks are the property of their respective owners.

ANSS-T

Commençons

Si vous êtes confronté à des défis d'ingénierie, notre équipe est là pour vous aider. Forts de notre expérience et de notre engagement en faveur de l'innovation, nous vous invitons à nous contacter. Collaborons pour transformer vos obstacles techniques en opportunités de croissance et de réussite. Contactez-nous dès aujourd'hui pour entamer la conversation.