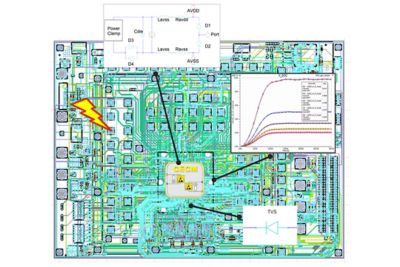

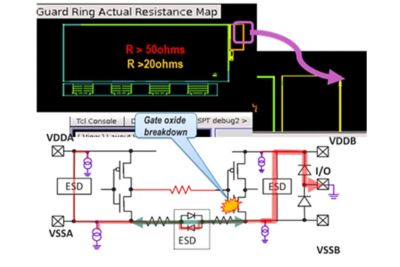

Lowering device breakdown voltages and interconnect dimensions poses increased ESD risk in sub 16nm processes. PathFinder-SC offers comprehensive analysis of on-chip ESD events, which is a requirement for all chip designs.

PathFinder-SC’s full-chip capacity and streamlined, single-pass use model can simultaneously handle hundreds of domains in one analysis. This is significantly faster than traditional approaches, speeding the time to results and reducing the potential for errors due to partitioning.

Any detected issues can be quickly debugged with PathFinder-SC’s layout-based analysis and Root Cause Detection technology, once again saving time and speeding time to market.

PathFinder-SC includes all capabilities in a single product – from performing RC extraction and ESD simulations, to analyzing root cause and providing optimization feedback. It includes a built-in RC extractor and requires no extra licenses or external tools.

PathFinder-SC is silicon-correlated by several customers and validated by multiple foundries which ensures accuracy and reduces silicon risk.