Applications

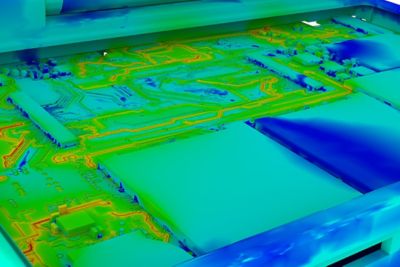

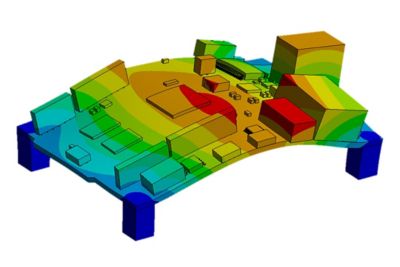

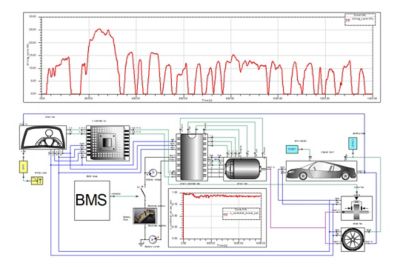

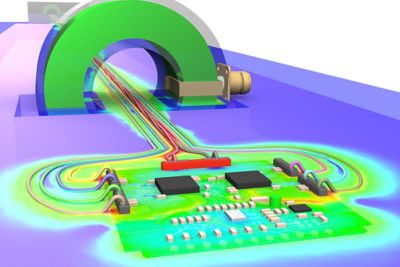

High tech electronics systems are the backbone for disruptive transformations occurring in industries ranging from mobility to energy, to the fourth industrial revolution and in silico healthcare. Ansys delivers high-tech electronics simulation applications spanning from the scale of silicon in semiconductor design and fabrication, to thermal and electronic reliability in packages and systems to electrically large environments such as cities.