Quick Specs

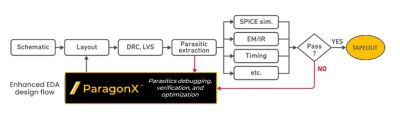

ParagonX is a process-agnostic tool that identifies parasitic-related design issues at an early layout stage, even before the design is LVS clean. Understanding the impact of layout parasitics is critical, especially for designs manufactured with advanced process nodes. This avoids productivity delays from performance bottlenecks and weak points later in the design process. With its unrivaled speed and capacity to handle huge netlists, IC layout engineers can find root causes and fix parasitic issues, leading to enhanced design quality and shorter design cycles.